MEMS Timing for Host Bus Adapters

| Devices | Key Features | Key Values |

|---|---|---|

|

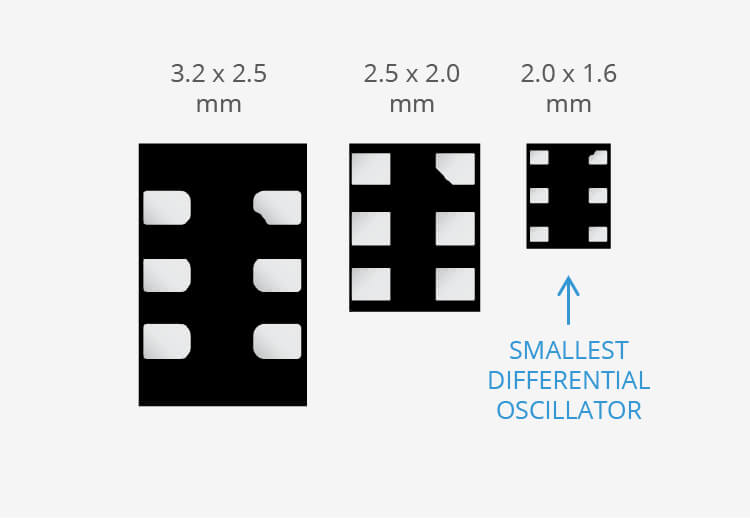

Differential Oscillators

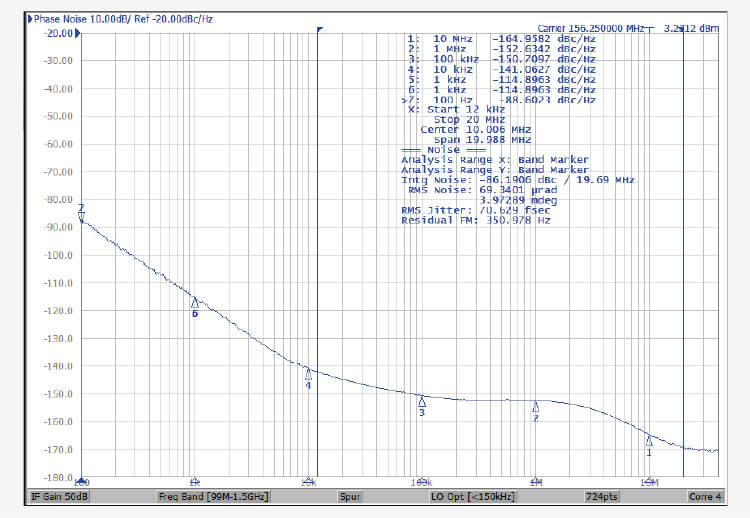

SiT9375 25 to 644.5 MHz, 70 fs Integrated Phase Jitter [1]

SiT9501 25 to 644.5 MHz, 150 fs Integrated Phase Jitter [1]

|

|

|

|

Clock Generator

SiT91211 1 to 750 MHz, 200 fs Integrated Phase Jitter [1]

SiT91213 1 to 750 MHz, 90 fs Integrated Phase Jitter [1]

|

|

|

[1] 12 kHz to 20 MHz integration range