156.25 MHz, ±0.1 to ±0.25 ppm Elite RF™ Differential-Ended Precision Super-TCXO

LoginThe SiT5977 is a differential ended ±100 ppb precision MEMS Super-TCXO® designed for high stability and low jitter applications, such as Smart NICs, acceleration cards, switches, and compute node applications.

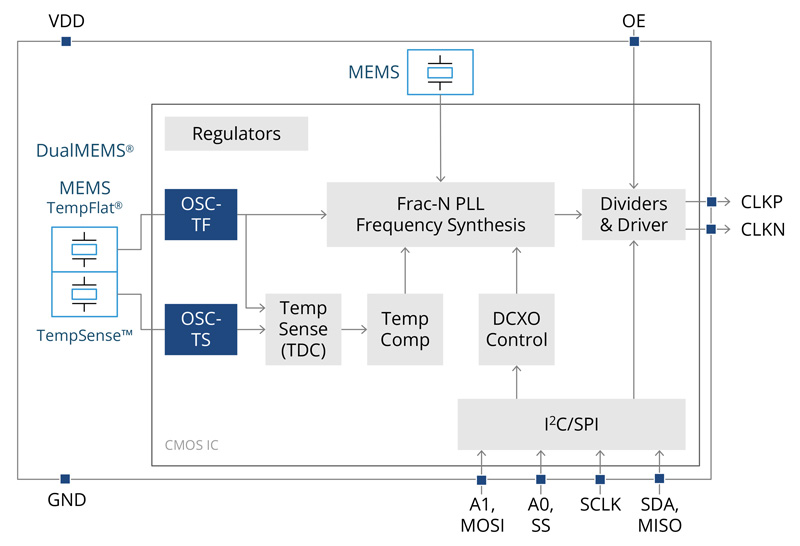

Combining SiTime’s DualMEMS® technology with a low-noise digital PLL, this chip delivers excellent jitter, dynamic stability in the presence of airflow and thermal excursions, and resistance to shock and vibration. Multiple on-chip regulators filter power supply noise, eliminating the need for an external LDOs.

The SiT5977 offers frequency control (DCTCXO) via an I2C/SPI interface with 0.05 ppt resolution and up to ±400 ppm pull range. This unique functionality, along with 80 fs phase jitter, can eliminate the need for a jitter cleaner and enable new architectural options.

Related Blog: Product Spotlight: SiT5977 Super-TCXO Enables New Architecture for Greater AI Workload Efficiency in Datacenters

| "Specs" | "Value" |

|---|---|

| Frequency | 156.25 MHz |

| Frequency Stability (ppm) | ±0.1, ±0.2, ±0.25 |

| Operating Temperature Range (°C) | -40 to +85 |

| Package Type (mm²) | 5.0 x 3.5, 10-pin |

| Phase Jitter (rms) | 80 fs |

| Pull Range (ppm) | ±3.125, ±6.25, ±10, ±12.5, ±25, ±50, ±100, ±200, ±400 |

| Voltage Supply (V) | 3.3 |

| Features | Best-in-class dynamic stability with ±1 ppb/°C frequency over temperature slope (dF/dT) |

| Availability | Pre-Production Sampling |

-

5032 10-Pin Ceramic MEMS Oscillator (Top & Bottom Angled View)

- Environmentally robust with ±1 ppb/°C frequency slope (dF/dT) for optimum performance under airflow, thermal shock

- Capable of driving 800G and higher links via 80 fs phase jitter and LVDS differential output

- Enables embedded control loops with precise digital tuning of output frequency (DCTCXO)

- Digital control via I2c/SPI

- Up to ±400 ppm pull range

- Frequency pull resolution down to 0.05 ppt (5e-14)

- Eliminates link flaps from activity dips or micro jumps associated with quartz devices

- Resistant to shock, vibration and board bending

- Eliminates external LDOs via on-chip voltage regulators

- ±100 ppb frequency stability over temperature with DualMEMS architecture

- 156.25 MHz output frequency enabling high-speed SerDes and 800G links

- Small 5.0 x 3.5 mm package (footprint compatible with 5.0 x 3.2 mm package)

- Contact SiTime for -40°C to 105°C operating temperature and other output options

To support system level synchronization, this chip integrates digital control (DCTCXO) via a I2C/SPI interface to adjust the output frequency with a fine resolution. Additionally, multiple on-chip regulators filter power supply noise, eliminating the need for an external LDO (low-dropout) regulator.

- Network Interface and Accelerator Cards

- Switches

- IEEE 1588 Boundary Clocks & Grandmasters

- SerDes

- 4G / 5G RRH, DU

- Small Cells

- RF Signal Chain

- Radar

- Satellite Base Station

- Microwave Backhaul

- Instrumentation

- Test & Measurement

- 5G Radios

Frequency Slope (dF/dT) Calculator – Calculate frequency slope over temperature

Time Error Simulation Software – Simulate and analyze the impact of the local oscillator

TimeMaster Configuration Software – Configure and evaluate oscillators via I2C/SP

Reliability Calculator – Get FIT/MTBF data for various operating conditions

SiTime Studio – A Phase-noise productivity tool

| Resource Name | Resource Type | Date | Format | Size |

|---|