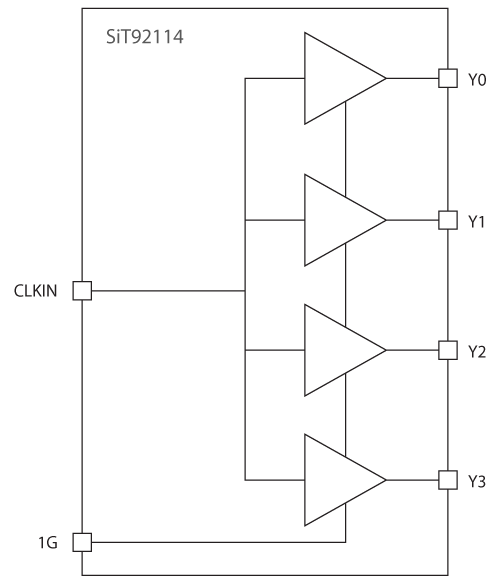

The SiT92114 is a high-performance LVCMOS fanout clock buffer with low additive phase jitter of 50 fs RMS.

The SiT92114 supports a synchronous glitch-free output enable (OE) function to eliminate potential intermediate incorrect output clock cycles when enabling or disabling outputs. It can operate from a 1.8 V to 3.3 V supply.

| "Specs" | "Value" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 2.0 x 2.0 8-pin DFN, 3.0 x 4.4 8-pin TSSOP |

| Buffer Type | Fanout |

| Number of Inputs | 1 |

| Number of Outputs | 4 Single Ended |

| Input Type | LVCMOS |

| Input Frequency Range | 0 Hz to 200 MHz |

| Output Type | LVCMOS |

| Output Frequency Range | 0 Hz to 200 MHz |

| Additive Phase Jitter (rms) | 50 fs |

| Propagation Delay, Typical | 1.0 ns |

| Output-Output Skew, Typical | 50 ps |

| Output Enable | Yes |

| Availability | Production |

-

2x2 mm, 8-pin DFN Clock Buffer package

- 3.3 V tolerant input clock.

- Integrated serial termination for 50 Ω channel.

- Wireless Base Stations

- 5G Infrastructure

- Telecom Equipment

- Computer Servers

SiT92114 Evaluation Board HW User Manual – Configure and evaluate device performance

Apply Filters

| Resource Name | Resource Type | Date | Format | Size |

|---|

Step 1: Enter or Configure SiT92114 Part Number

Step 2. Purchase

Quantity

| Qty: | Unit Price | Total |

|---|---|---|

| --- | --- | --- |

| Quantity | Unit Price | |

|---|---|---|

| 199 | --- | |

| 100-499 | --- | |

| 500-999 | --- | |

| 1,000-4,999 | --- | |

| > 4,999 | --- |