FPGAs have evolved well beyond their original logic and flip-flop-based fabric with general-purpose I/O. Modern FPGAs integrate embedded memory, DSP blocks, AI processors, and a network-on-chip for high-speed interconnectivity. Many also feature multi-core processors, often optimized for AI/ML workloads.

The I/O ring has also advanced, incorporating hard IP blocks and high-speed SerDes to support interfaces such as Gigabit Ethernet, PCIe, and DDR memory. These additions enable increasingly complex clocking requirements in modern FPGAs.

FPGAs Represent a Complex Clocking Environment

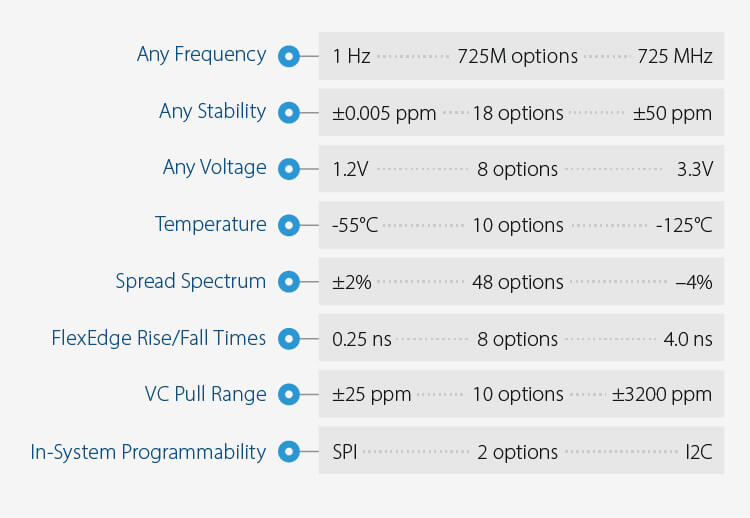

Expanding FPGA functionality has introduced more complex clocking requirements. To address these demands, FPGA vendors integrate multiple PLLs and clock management features, driving demand for diverse clock sources, including:

- Reference clocks for SerDes transceivers with stringent phase noise requirements

- Timekeeping and timestamping for RTCs, IEEE 1588, and GNSS-based applications

- Multiple reference clocks for embedded PLLs

- Per I/O bank reference clocks

- Clocks for user logic

- Supporting clock sources for configuration controllers, low-speed interfaces, and other system functions

SRAM-based FPGAs often require external logic for configuration, typically using a small CPU and flash memory, each with its own clock source.

FPGAs and their configuration logic operate alongside high-performance CPUs, FPGA-based accelerators, transceivers, DRAM, and other ASSPs—each with distinct clocking needs. This creates a complex timing environment, requiring a supplier that provides a full range of clocking solutions, from oscillators to advanced clock management devices.

FPGAs are Ubiquitous

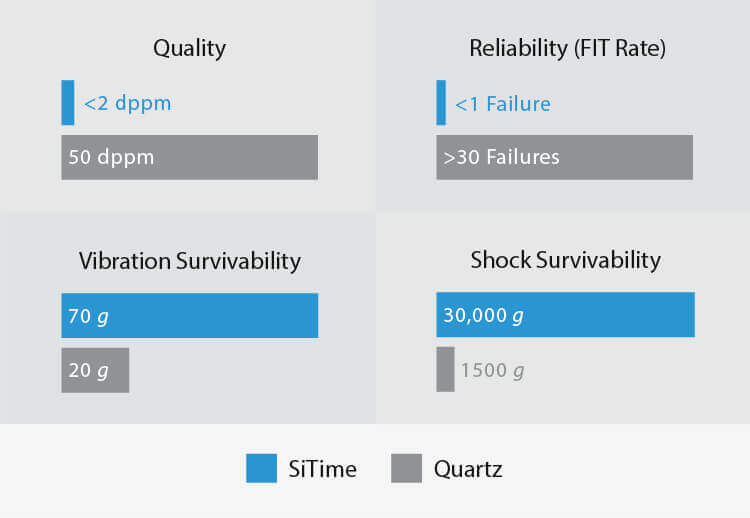

FPGAs are used in diverse applications, from set-top boxes and GPS-guided munitions to the ocean floor and space. They provide customizable solutions where integrating a custom ASIC is impractical due to high NRE costs or tight time-to-market constraints. To ensure safe, reliable operation, FPGA designers rely on suppliers with product lines that support a broad environmental spectrum—from stable enterprise conditions to deployments exposed to wide temperature variations, high vibration, and intense pressure.