Wenn Sie ein PDF dieser Anwendungsnotiz [AN10029] herunterladen möchten, klicken Sie hier .

1. Einleitung

Differentialoszillatoren werden in Hochleistungsanwendungen eingesetzt und bieten mehrere Vorteile, wie z. B. eine höhere Robustheit gegenüber Netzteilrauschen. Dieser Anwendungshinweis enthält Abschlussempfehlungen für die in Tabelle 1 aufgeführten SiTime-Differentialoszillatorfamilien mit LVPECL-, LVDS- oder HCSL-Ausgangstreibern. Schnittstellen zum Ansteuern von CML- oder HCSL-Takteingängen mit LVPECL-Ausgang werden ebenfalls besprochen.

Typische Ausgangsanstiegs- und -abfallzeiten von SiTime-Oszillatoren liegen im Bereich von 250 ps bis 600 ps, was dazu führt, dass sich selbst kurze Leiterbahnen auf einer Leiterplatte wie verteilte Übertragungsleitungen verhalten, die eine Impedanzanpassung erfordern. Daher wird empfohlen, Leiterbahnen für Differenzsignale als Übertragungsleitungen mit kontrollierter Impedanz und angepasster Länge zu entwerfen. Diese Leiterbahnen sollten für beste Signalintegrität und niedrigste EMI ordnungsgemäß abgeschlossen werden. Zusätzlich zur Impedanzanpassung wirken sich Abschlussnetzwerke auch auf die Gleichstromvorspannung und den Wechselspannungshub auf der Empfängerseite aus.

Tabelle 1: SiTime-Differenzoszillatoren

Gerätefamilie | Oszillatortyp | Ausgangstreibertypen |

Differentialoszillatoren | LVPECL, LVDS | |

Differentialoszillatoren | LVPECL, LVDS | |

Differentialoszillatoren | LVPECL, LVDS | |

SiT9365 | Hochleistungs-Differenzoszillatoren | LVPECL, LVDS, HCSL |

Hochleistungs-Differenzoszillatoren | LVPECL, LVDS, HCSL | |

Hochleistungs-Differenzoszillatoren | LVPECL, LVDS, HCSL | |

Hochleistungs-Differenzoszillatoren für die Automobilindustrie | LVPECL, LVDS, HCSL | |

Hochleistungs-Differenzoszillatoren für die Automobilindustrie | LVPECL, LVDS, HCSL | |

Spannungsgesteuerte Oszillatoren (VCXO) mit DE | LVPECL, LVDS | |

SiT3822 | Spannungsgesteuerter Oszillator (VCXO) mit DE | LVPECL, LVDS |

Hochleistungsfähige spannungsgesteuerte Oszillatoren (VCXO) mit DE | LVPECL, LVDS, HCSL | |

Hochleistungsfähige spannungsgesteuerte Oszillatoren (VCXO) mit DE | LVPECL, LVDS, HCSL | |

Spannungsgesteuerte Oszillatoren (VCXO) mit DE | LVPECL, LVDS | |

Spannungsgesteuerte Oszillatoren (VCXO) mit DE | LVPECL, LVDS | |

Hochleistungs-Spread-Spectrum-Oszillatoren (SSXO) mit DE | LVPECL, LVDS, HCSL, CML | |

Hochleistungsfähige digital gesteuerte Oszillatoren (DCXO) mit DE | LVPECL, LVDS, HCSL | |

Hochleistungsfähige digital gesteuerte Oszillatoren (DCXO) mit DE | LVPECL, LVDS, HCSL | |

Temperaturgesteuerte Oszillatoren (TCXO) mit DE | LVPECL, LVDS | |

Temperaturgesteuerte Oszillatoren (TCXO) mit DE | LVPECL, LVDS |

2. LVPECL-Ausgabe

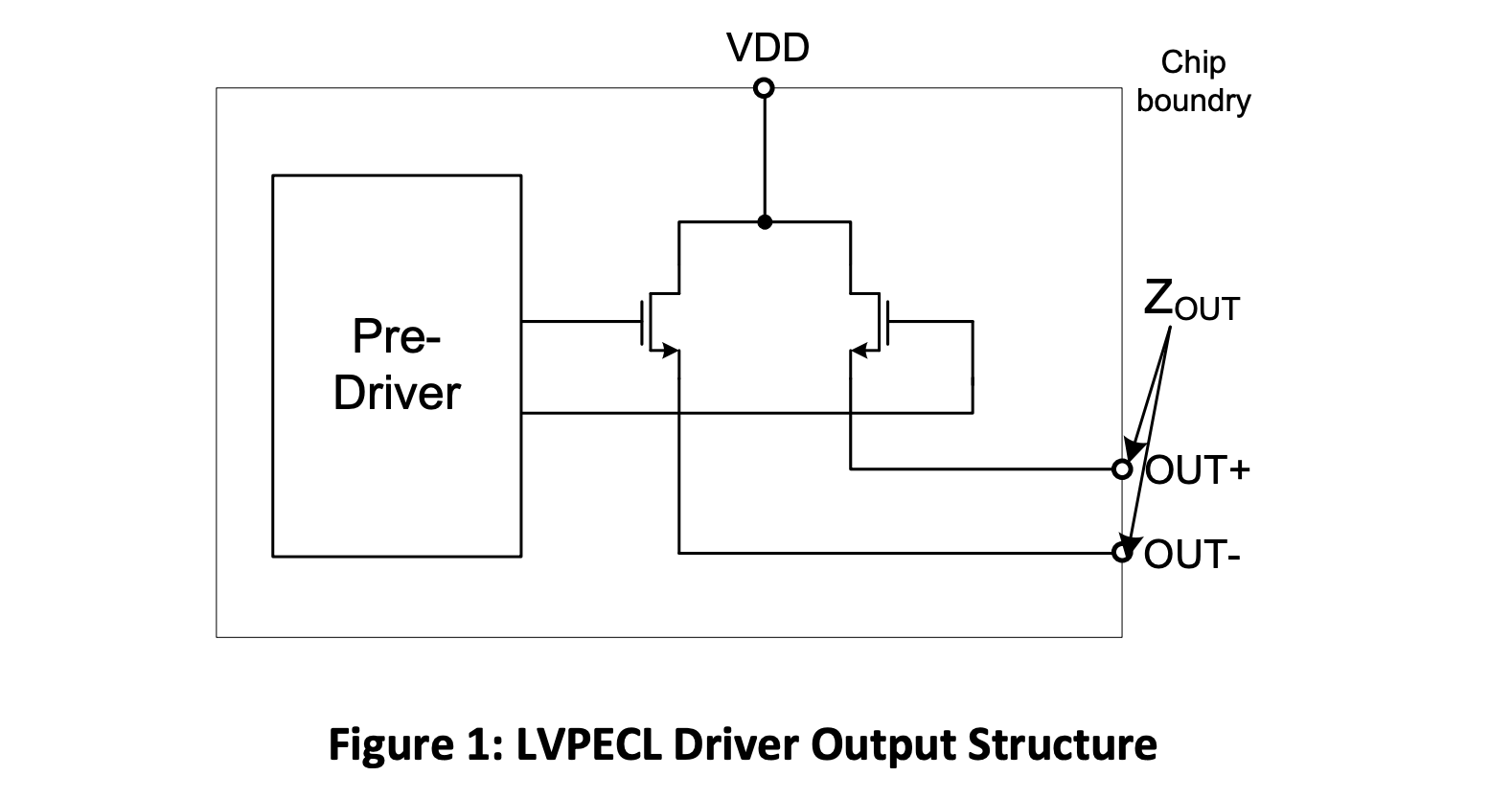

Abbildung 1 zeigt eine LVPECL-Treiberstruktur mit niedriger Impedanz, die in SiTime-Differentialoszillatorfamilien verwendet wird. Eine Ausgangsstufe eines Treibers besteht aus einem Paar NMOS-Transistoren in Common-Source-Konfiguration. Die typische Treiberimpedanz beträgt etwa 5 Ω bis 10 Ω.

2.1 Terminierungsempfehlungen für DC-gekoppelte Anwendungen

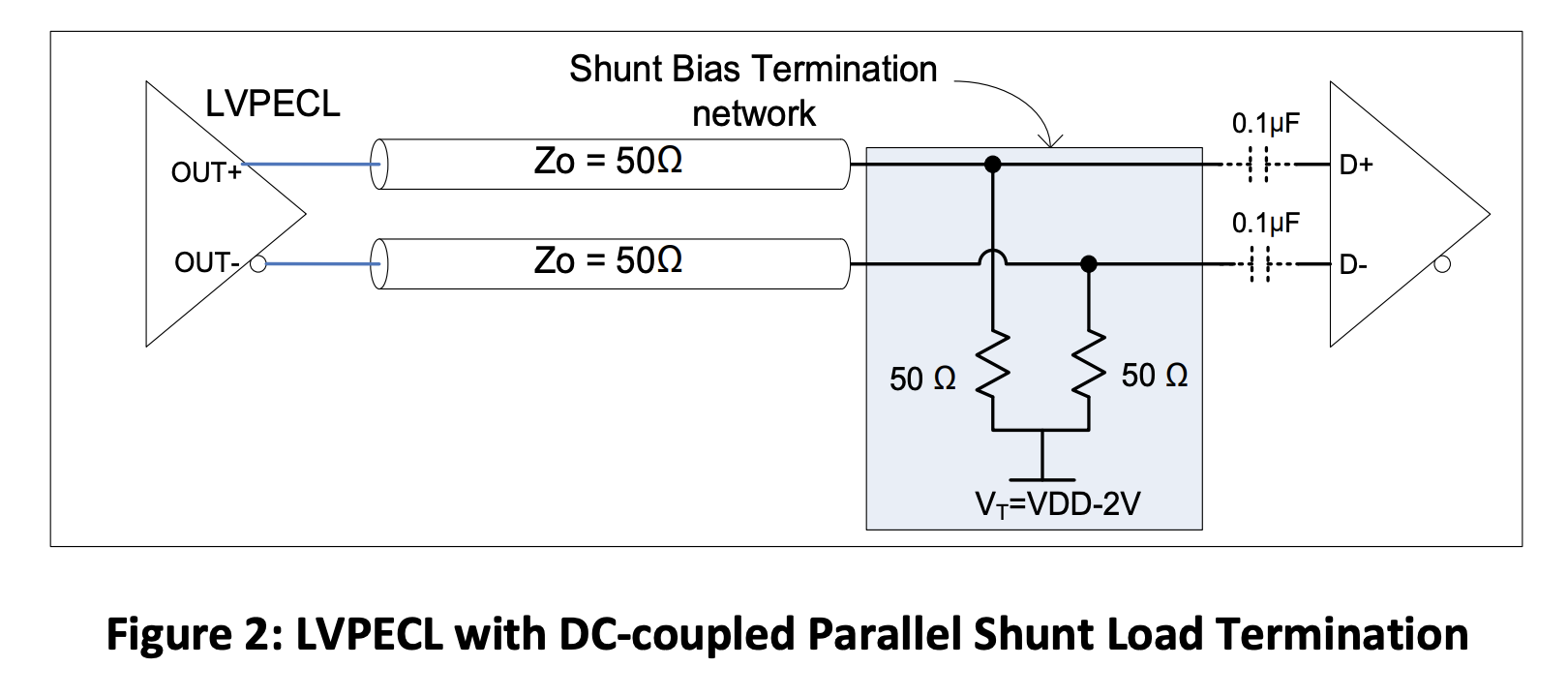

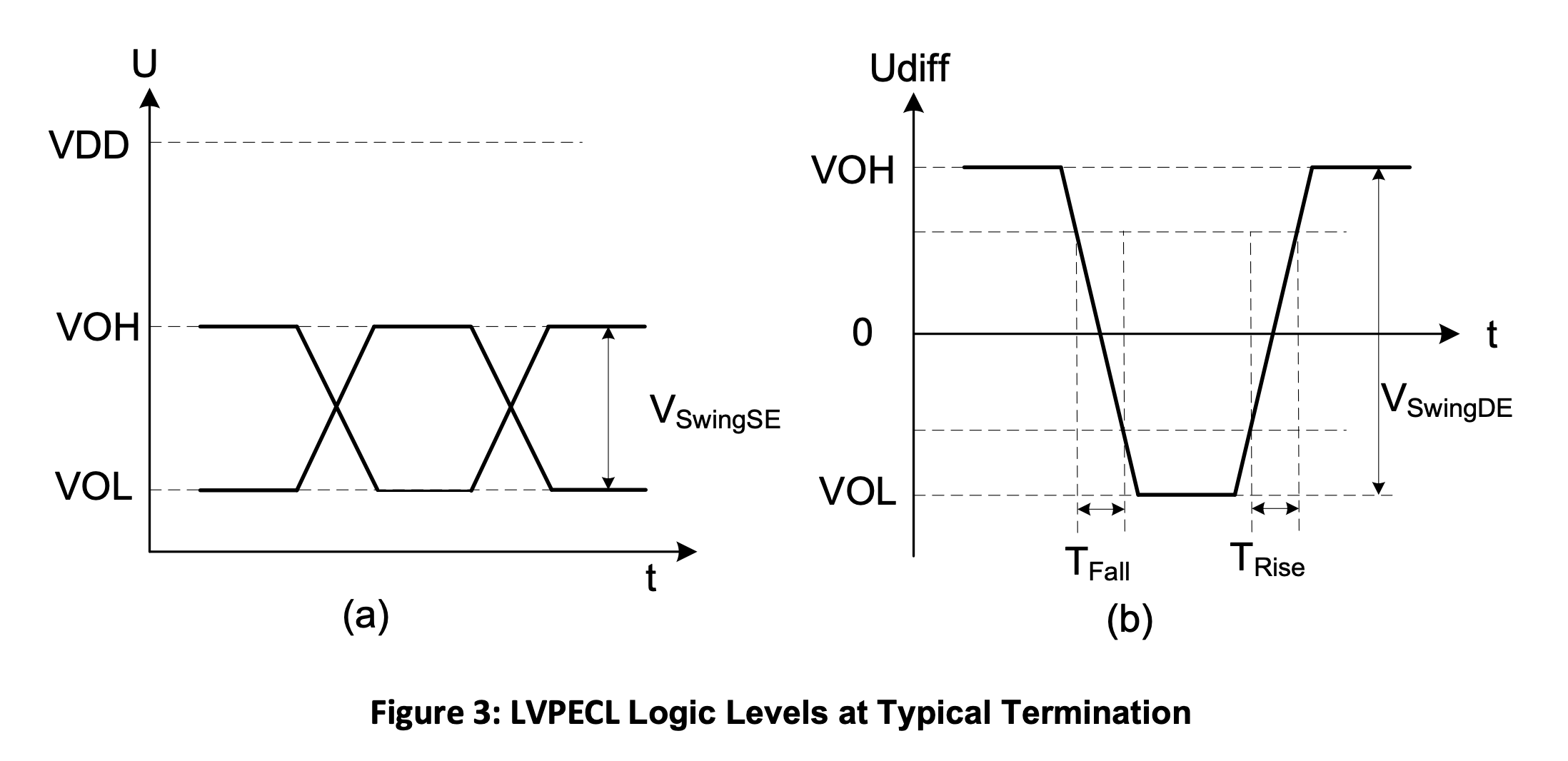

LVPECL wird normalerweise auf der Lastseite abgeschlossen, wie in Abbildung 2 dargestellt. Die Ausgänge sind mit 50-Ω-Widerständen an eine Abschlussspannung (VT) angeschlossen, was eine gute Impedanzanpassung an die Übertragungsleitung gewährleistet (siehe Anhang A für die Lastabschlussanalyse). Abbildung 3(a) zeigt eine Single-Ended-Wellenform des LVPECL-Ausgangs mit typischer Terminierung. Die typischen Signalpegel für den hohen Spannungsausgang (VOH) und den niedrigen Spannungsausgang (VOL) betragen VDD – 0,9 V bzw. VDD – 1,7 V. Die im Datenblatt angegebenen VOH- und VOL-Grenzwerte berücksichtigen Schwankungen der Ausgangstreiberimpedanz von Teil zu Teil und externe Lastbedingungen.

Der Spannungshub der Differenzwellenform zwischen positiven und negativen Ausgängen (VDiff = VOUT+ -VOUT-) ist doppelt so groß wie die Spannungsamplitude des Single-Ended-Signals. Der typische LVPECL-Differenzhub beträgt 1,6 V. Abbildung 3(b) zeigt, wie Anstiegs- und Abfallzeiten von 20 % bis 80 % für eine Differenzwellenform definiert werden.

Beachten Sie, dass VOH, VOL und Spannungshub von der Terminierung abhängen und unterschiedlich sein können, wenn eine nicht standardmäßige Terminierung verwendet wird.

Wenn ein LVPECL-Empfänger nicht über einen integrierten Abschluss verfügt, sollten externe 50-Ω-Abschlusswiderstände so nah wie möglich am Empfänger platziert werden, um nicht abgeschlossene Stichleitungen zu reduzieren, die Probleme mit der Signalintegrität verursachen können. Eine Übertragungsleitung sollte nur auf der Lastseite abgeschlossen werden.

In Anwendungen, in denen eine separate Abschlussspannung nicht ohne weiteres verfügbar ist, können Pull-Up- und Pull-Down-Widerstände, die ein Thevenin-Äquivalent-Netzwerk bilden, zum Abschluss von 50-Ω-Übertragungsleitungen verwendet werden (siehe Abbildung 4). Ein solches Netzwerk erzeugt eine Gleichstromvorspannung von VDD – 2 V an den Empfängereingängen und eine effektive Abschlussimpedanz von 50 Ω. Beachten Sie, dass die Widerstandswerte für Versorgungsspannungen von 3,3 V und 2,5 V unterschiedlich sind.

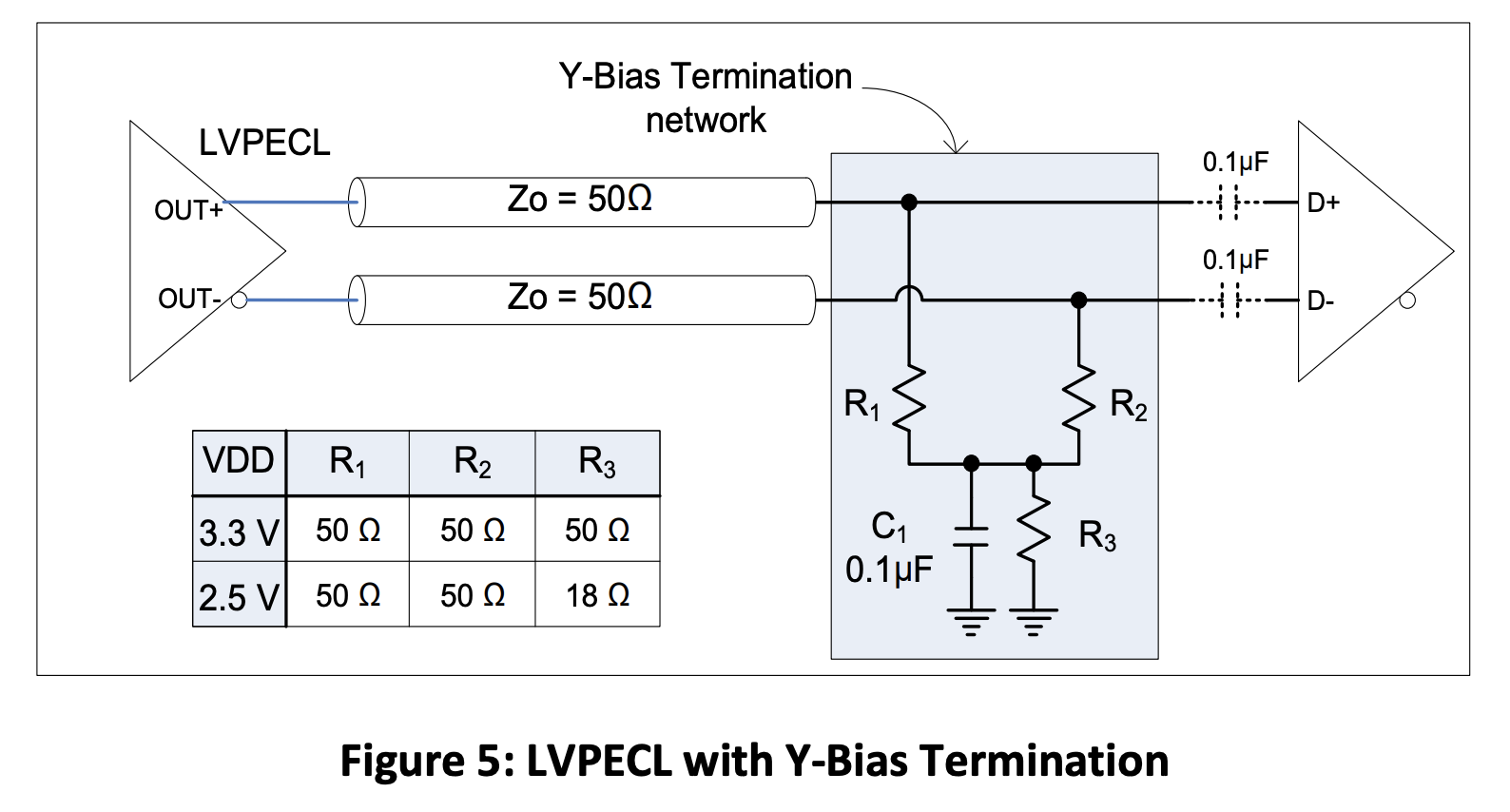

In den meisten Fällen funktioniert die äquivalente Terminierung von Thevenin gut, sie kann jedoch empfindlich auf Stromversorgungsrauschen reagieren, wenn zwischen den Leiterbahnen oder zwischen Widerstandsnetzwerken auf jeder Seite des Differentialpaars eine signifikante Diskrepanz besteht oder wenn der Empfänger zu empfindlich auf Gleichtaktrauschen reagiert . Abbildung 5 zeigt das Y-Bias-Abschlussnetzwerk, das eine effektive Abschlussspannung von VDD – 2 V bereitstellt, ohne dass eine Verbindung zu VDD oder Zugriff auf eine zusätzliche Abschlussspannungsquelle erforderlich ist. Die Abschlussspannung wird durch die Summe der Differenzpaarströme erzeugt, die durch den Widerstand R3 fließen. Der Kondensator C1 dient zur Erzeugung einer Wechselstrommasse bei der Abschlussspannung.

2.2 Terminierungsempfehlungen für AC-gekoppelte Anwendungen

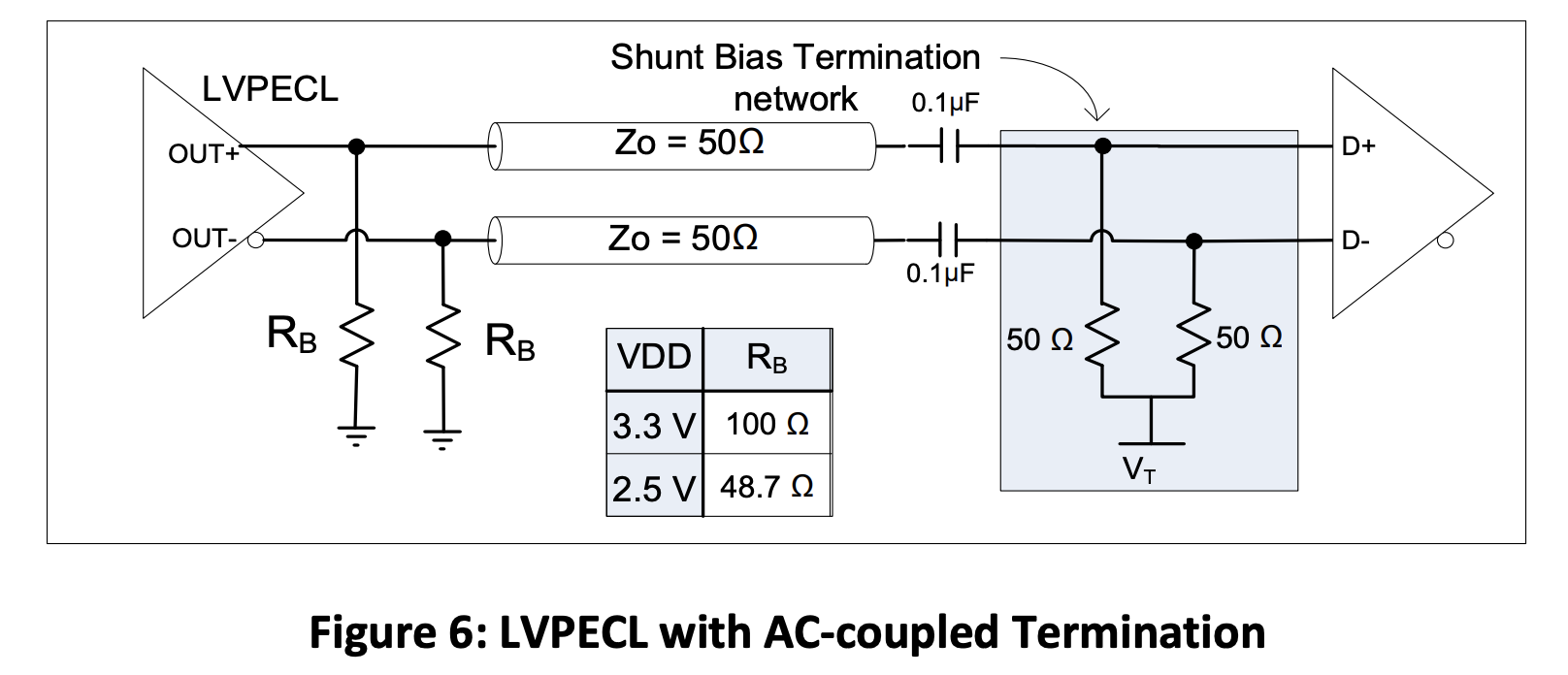

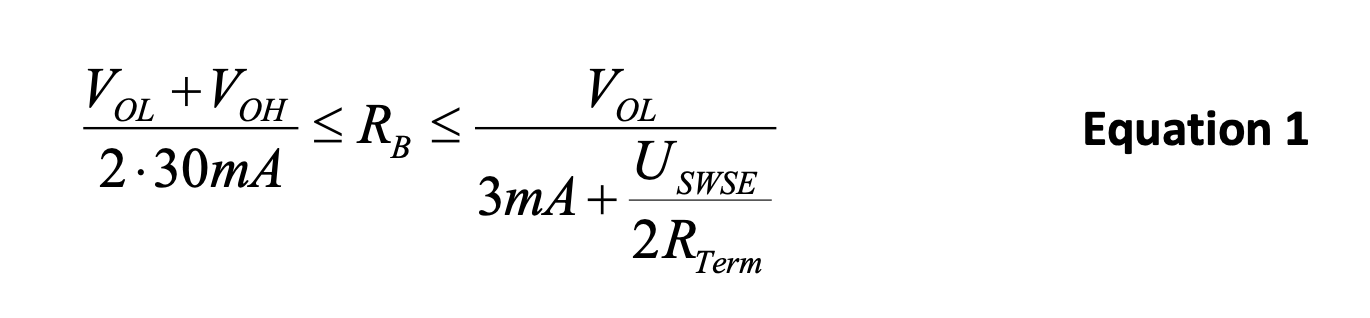

Ein LVPECL-Empfänger kann entweder DC- oder AC-gekoppelt sein. AC-Koppelkondensatoren sind erforderlich, wenn die DC-Vorspannungen auf Empfänger- und Oszillatorseite unterschiedlich sind. In einigen Fällen muss ein Abschlussnetzwerk wechselstromgekoppelt sein, wie in Abbildung 6 dargestellt. Für den ordnungsgemäßen Betrieb des LVPECL-Treibers sollten seine Ausgangstransistoren niemals vollständig ausgeschaltet werden. Daher sind zusätzliche Vorspannungswiderstände RB erforderlich, die vor den Wechselstromkopplungskondensatoren platziert werden um einen Gleichstrompfad für den Treiber bereitzustellen. Der Wert von RB wird so gewählt, dass der minimale Strom durch einen Treiber-Pin, wenn sich der Pin im Low-Zustand befindet, nicht weniger als 3 mA beträgt und der maximale Gleichstrom durch einen Treiber 30 mA nicht überschreitet. Gleichung 1 kann zur Schätzung von RB verwendet werden.

In Gleichung 1 ist USWSE der Single-Ended-Spannungshub und RTerm der Abschlusswiderstand des Netzwerks. SiTime empfiehlt die Verwendung von RB-Werten von 100 Ω und 48,7 Ω für eine 3,3-V- bzw. 2,5-V-Versorgung.

Die folgenden Empfehlungen sollten befolgt werden, um die beste Signalintegrität mit LVPECL-Parallellastabschlüssen zu erreichen:

- Platzieren Sie das Abschlussnetzwerk in einem Abstand von 0,1 bis 0,2 Zoll vom Empfänger. Lange Leiterbahnen, die das Abschlussnetzwerk mit dem Empfänger verbinden, erscheinen als Stichleitungen und können die Signalintegrität an den Empfängereingängen beeinträchtigen.

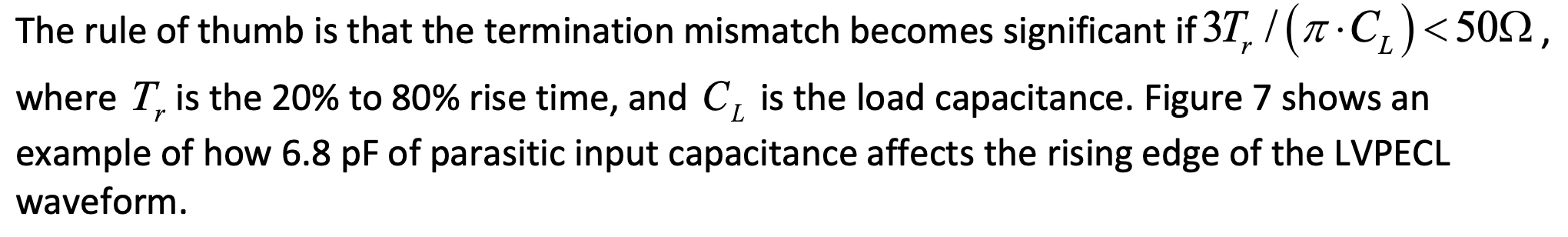

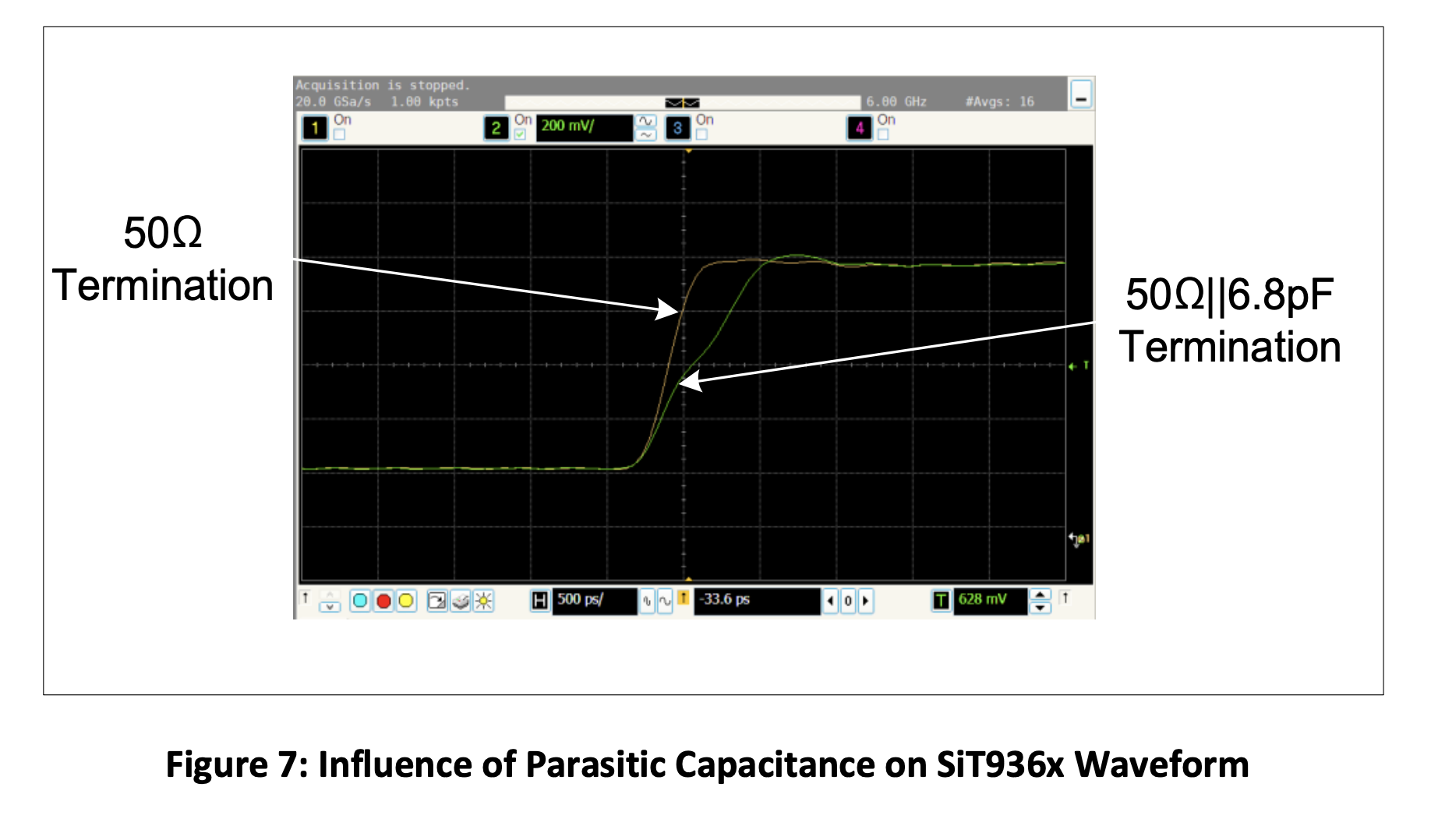

- Minimieren Sie kapazitive Lasten am Empfängereingang. Hohe kapazitive Lasten reduzieren die Abschlussimpedanz, wenn schnelle Signalflanken den Empfänger erreichen, was zu einem großen Lastreflexionskoeffizienten führt. Diese Reflexion kehrt mit etwas Dämpfung zur Last zurück, nachdem sie an der Quelle reflektiert wurde.

3. LVDS-Ausgabe

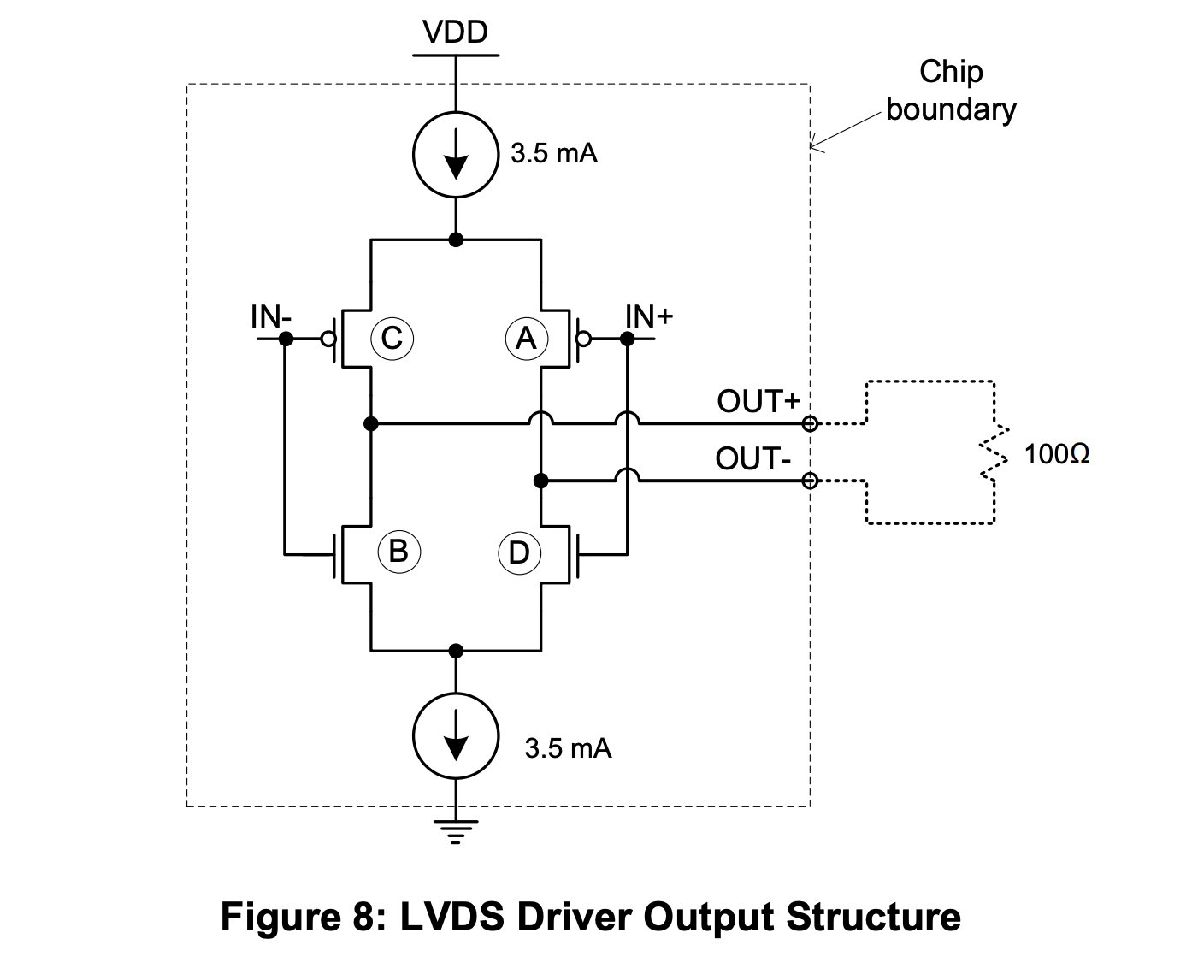

LVDS ist eine digitale Hochgeschwindigkeitsschnittstelle, die für viele Anwendungen geeignet ist, die einen geringen Stromverbrauch und eine hohe Störfestigkeit erfordern. LVDS-Ausgänge nutzen Differenzsignale mit geringen Spannungsschwankungen, um Daten mit hohen Raten zu übertragen. Abbildung 8 zeigt die Ausgangsstruktur eines LVDS-Treibers, bestehend aus 3,5-mA-Nennstromquellen, die über ein Schaltnetzwerk, manchmal auch als „H“-Schalter bezeichnet, mit Differenzausgängen verbunden sind. Die Ausgänge sind typischerweise mit 100-Ω-Differenzübertragungsleitungen verbunden, die mit einem 100-Ω-Widerstand über den Empfängereingängen abgeschlossen sind. Der Widerstandswert passt sich der Impedanz der Übertragungsleitungen an und stellt einen Strompfad für das Signal bereit.

Der Treiber enthält eine Schaltung, um den Gleichtakt unabhängig von VDD auf nominell 1,2 V einzustellen. Daher besteht keine Notwendigkeit, den Treiber extern auf eine bestimmte Spannung vorzuspannen. Außerdem kann ein LVDS-Ausgang mit jedem LVDS-Eingang verbunden werden, ohne dass die tatsächliche Versorgungsspannung des Oszillators berücksichtigt werden muss.

Die Signalumschaltung erfolgt über vier Transistoren mit den Bezeichnungen A, B, C und D. Da die Impedanz des Empfängers typischerweise hoch ist, fließt praktisch der gesamte Strom vom Treiber durch den 100-Ω-Widerstand, was zu einer Spannungsdifferenz von 350 mV zwischen dem Empfänger führt Eingänge. In Abbildung 8 sind die Transistoren A und B eingeschaltet, wenn das Signal IN niedrig ist. Der Strom fließt durch Transistor A und den 100-Ω-Widerstand und kehrt durch Transistor B zurück. Wenn das Signal IN hoch ist, sind die Transistoren C und D eingeschaltet; Der Strom fließt durch Transistor C und den 100-Ω-Widerstand und kehrt durch Transistor D zurück, was zu einer Spannung von -350 mV am Empfänger führt.

Aus Empfängersicht bestimmt die Richtung des durch den Abschlusswiderstand fließenden Stroms, ob eine positive oder negative Differenzspannung registriert wird. Eine positive Differenzspannung stellt einen logisch hohen Pegel dar, während eine negative Differenzspannung einen logisch niedrigen Pegel darstellt.

3.1 Terminierungsempfehlungen für DC-gekoppelte Anwendungen

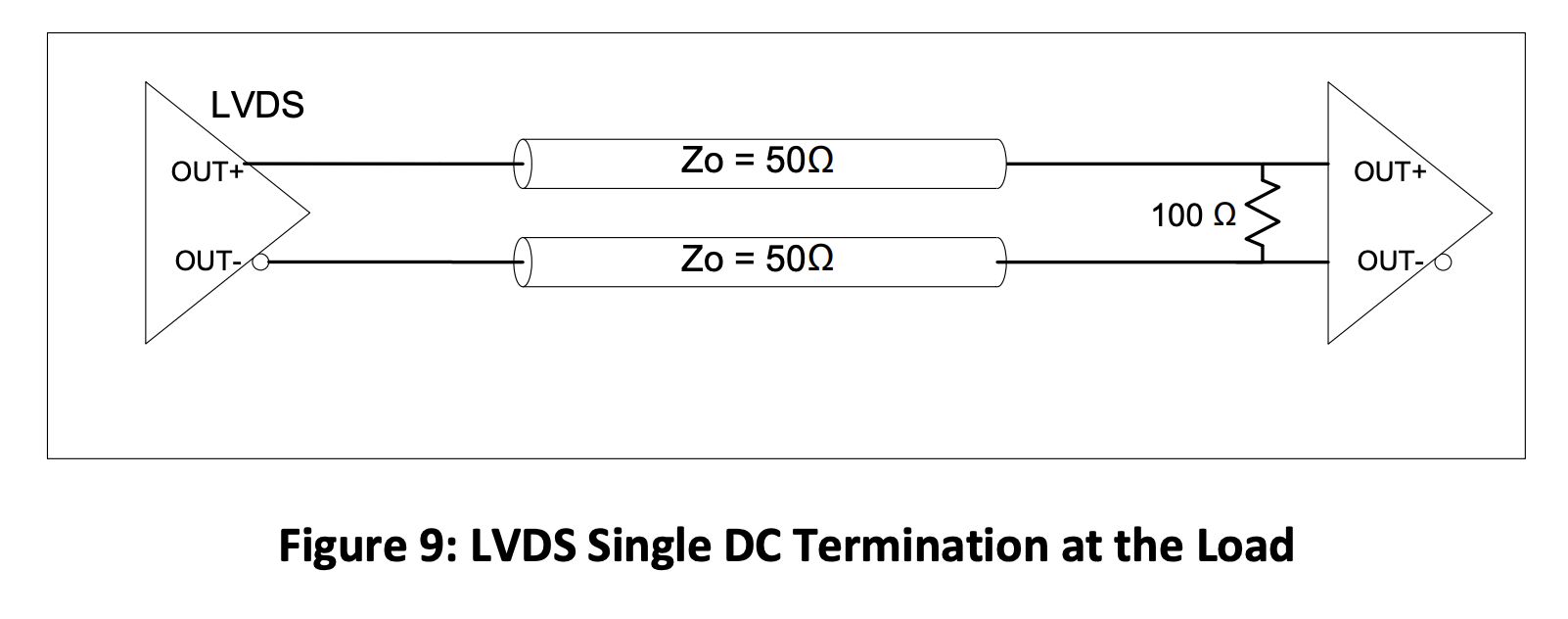

Eine LVDS-Schnittstelle mit 100-Ω-Differenzleiterbahnen wird normalerweise auf der Empfängerseite mit einem 100-Ω-Widerstand über den Differenzeingängen des Empfängers abgeschlossen (siehe Abbildung 9). Einige Empfänger verfügen über einen 100-Ω-On-Chip-Widerstand, sodass kein externer Abschluss erforderlich ist.

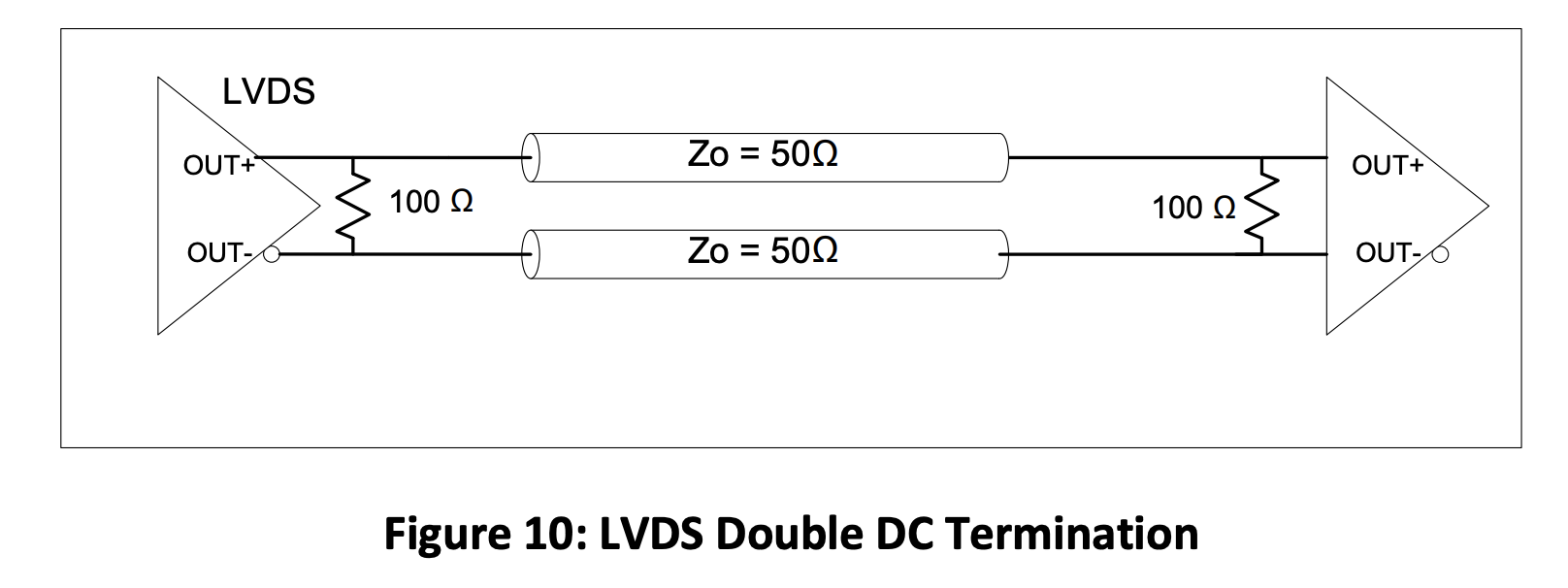

Für die meisten Anwendungen ist ein einzelner Abschluss an der Last ausreichend. In Situationen, in denen der Lastreflexionskoeffizient relativ hoch ist, kann eine Doppelabschlussanordnung den Gesamtumlauf verringern (siehe Abbildung 10). Mit einem 100-Ω-Widerstand sowohl an der Quelle als auch an der Last wird der äquivalente Widerstand am Ausgangstreiber auf 50 Ω reduziert, wodurch der Ausgangssignalhub halbiert wird.

3.2 Terminierungsempfehlungen für AC-gekoppelte Anwendungen

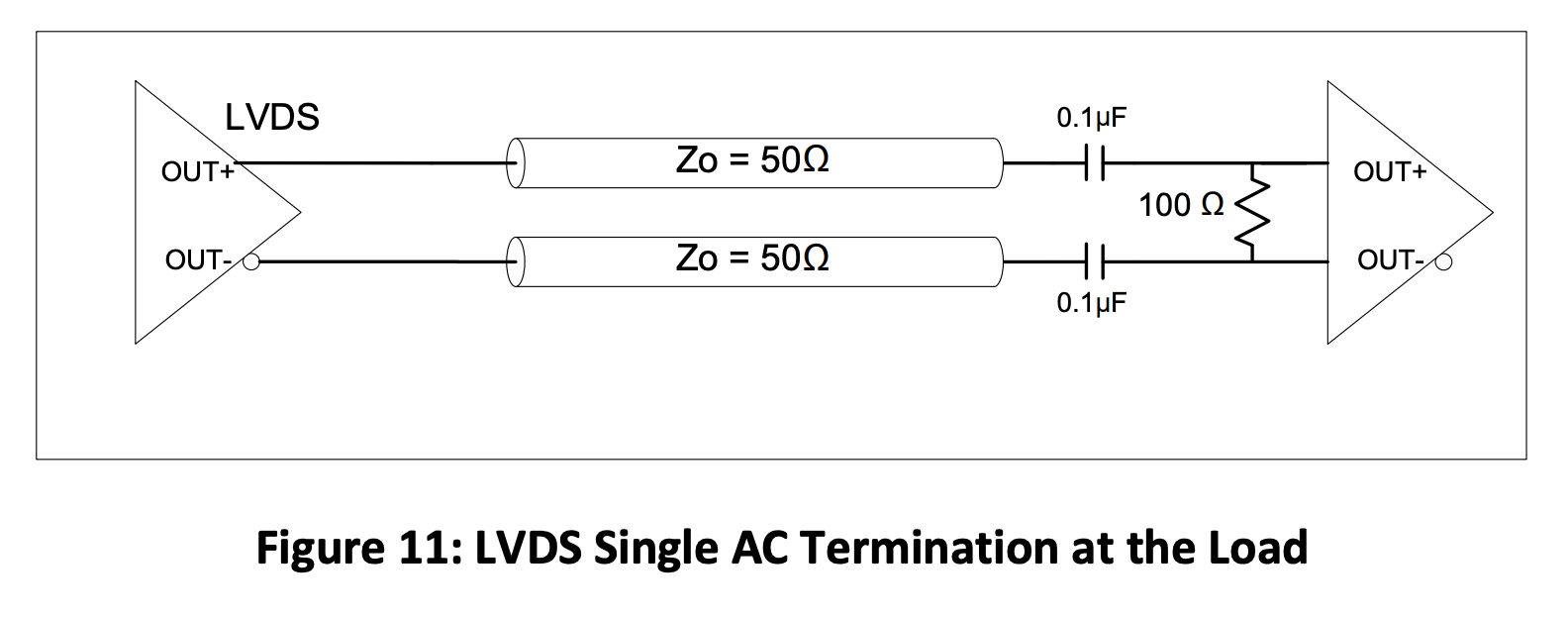

Wenn ein LVDS-Treiber und -Empfänger mit unterschiedlichen Gleichtaktspannungen betrieben werden, wird ein AC-Abschluss empfohlen. Ein Kondensator wird verwendet, um den Gleichstrompfad vom Treiber zu blockieren, daher muss der Empfänger eine eigene Eingangsvorspannungsschaltung implementieren.

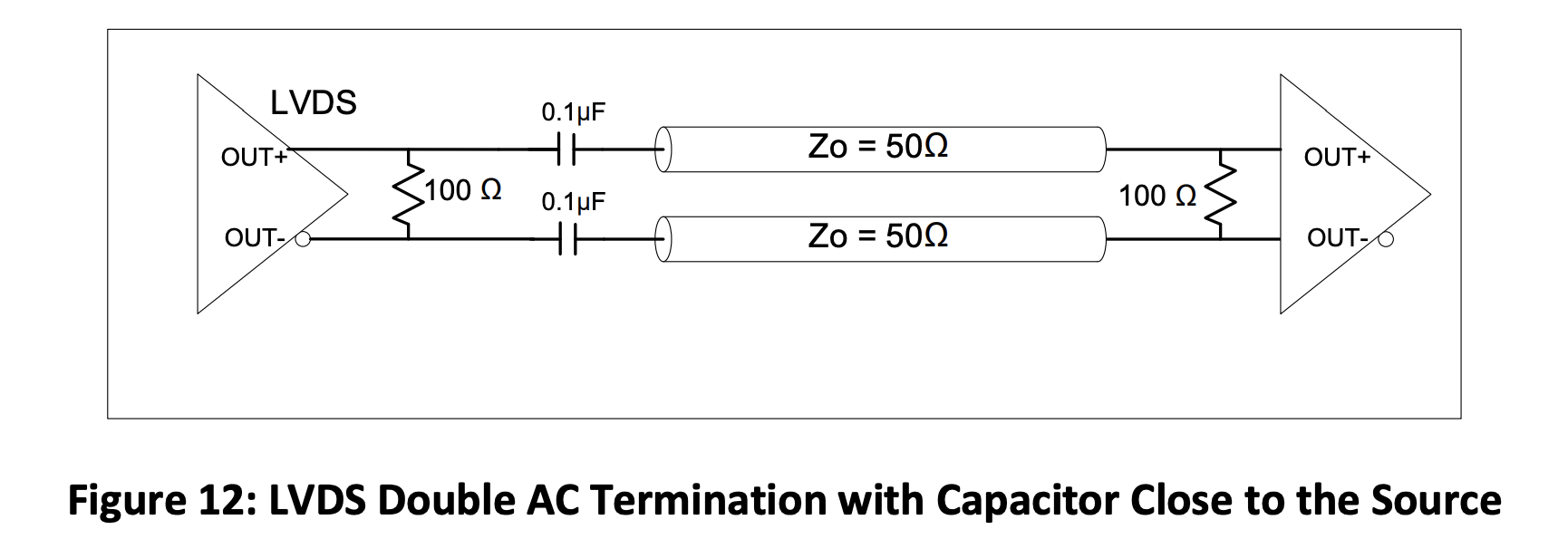

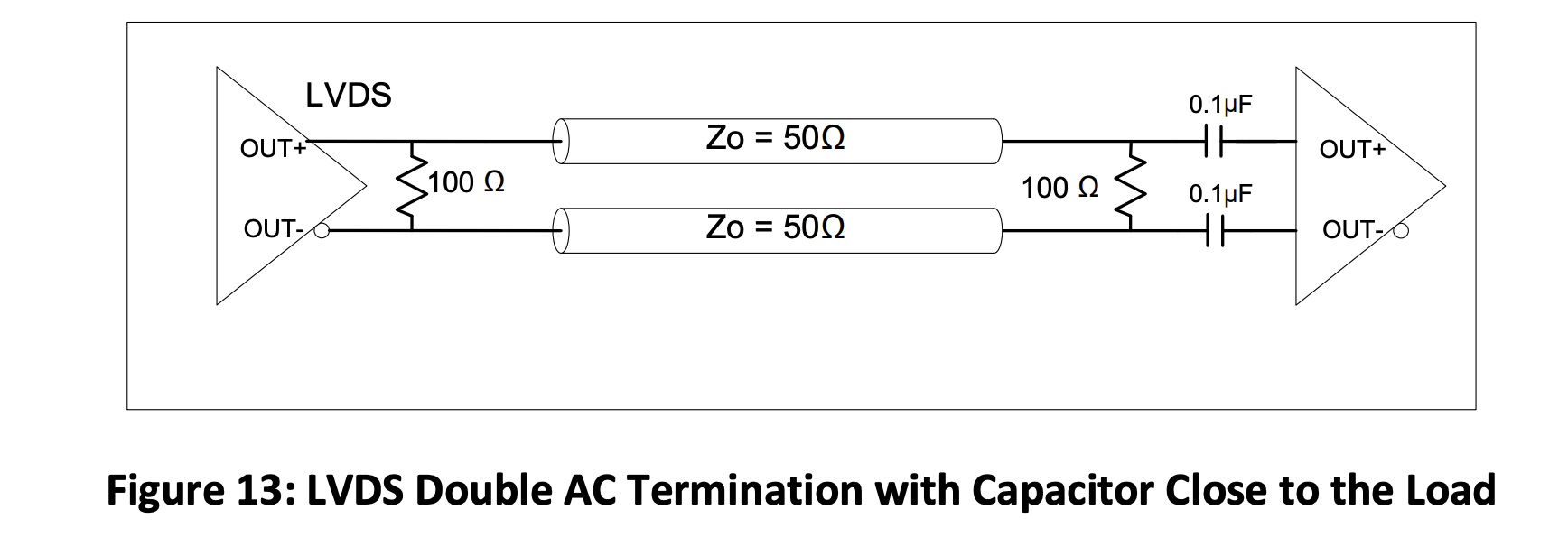

Die AC-Kopplung kann entweder als Einzelabschluss an der Last oder als Doppelabschluss konfiguriert werden. Der Einzelabschluss ist in Abbildung 11 dargestellt. Sowohl bei Einzel- als auch bei Doppelabschlüssen können AC-Kopplungskondensatoren vor (dargestellt in Abbildung 12) oder nach (dargestellt in Abbildung 13) dem Lastabschlusswiderstand platziert werden.

Die in (Abbildung 12 und Abbildung 13) gezeigten Doppelanschlüsse unterscheiden sich nur in der Position des AC-Koppelkondensators. Der Kondensator in Abbildung 12 wird durch den Gleichtaktstrom geladen, der durch den halben Differenzwiderstand fließt, was 50 Ω entspricht. Der Kondensator in Abbildung 13 wird durch den Strom durch den Widerstand der Empfängereingänge geladen, der im Bereich von mehreren zehn Kiloohm liegen kann. Während des Taktstarts wird der in Abbildung 12 gezeigte Kondensator viel schneller aufgeladen als der in Abbildung 13 gezeigte. Daher steht dem Empfänger früher ein gültiges Taktsignal zur Verfügung. Wenn ein schneller Taktstart wichtig ist, ist die in Abbildung 12 gezeigte Konfiguration vorzuziehen.

Bei Datenübertragungsanwendungen kann die in Abbildung 13 gezeigte Konfiguration vorteilhafter sein. Aufgrund seiner höheren RC-Zeitkonstante kann er Datensequenzen mit längeren Einsen und Nullen ohne nennenswerten Spannungsabfall aufrechterhalten.

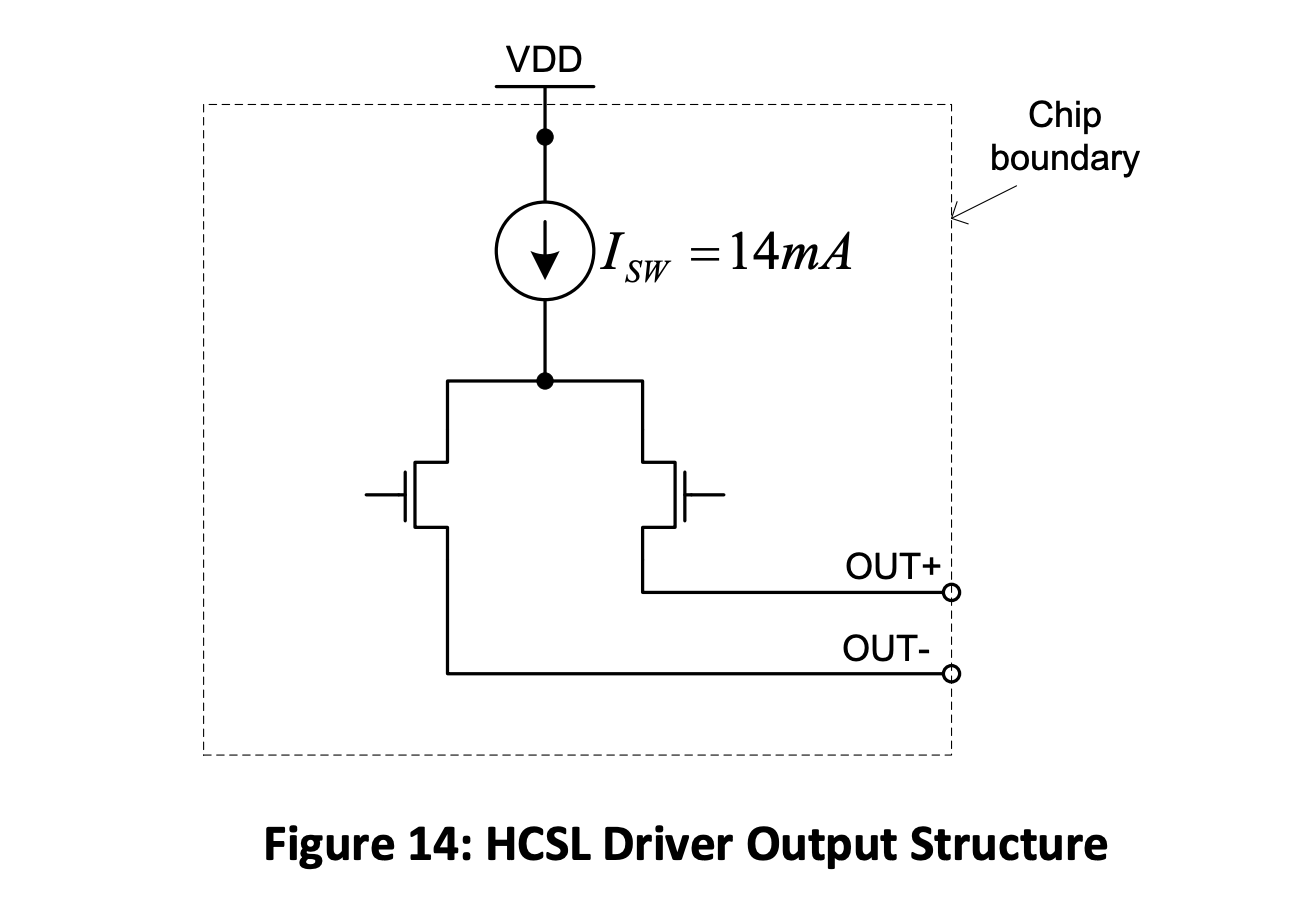

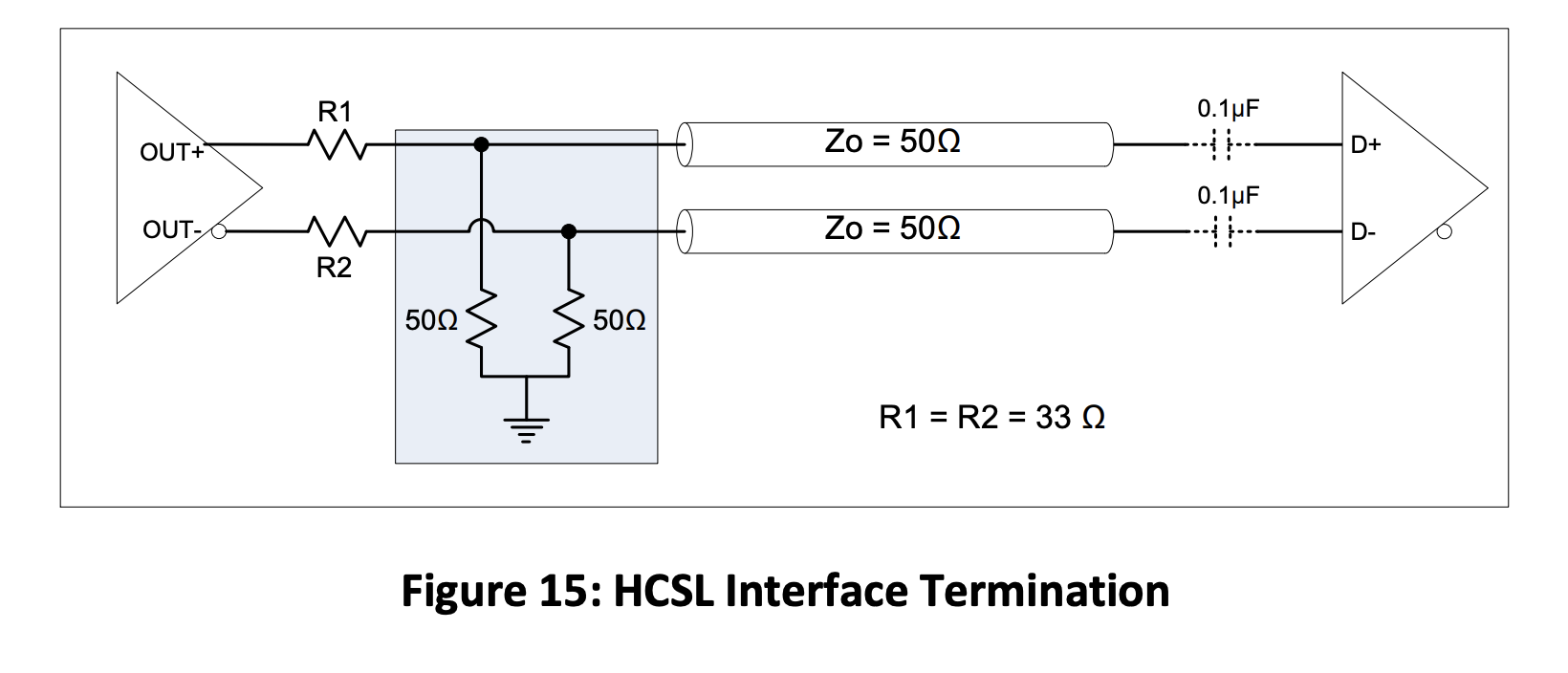

4. HCSL-Ausgabe

Die HCSL-Treiberoption ist nur in einigen SiTime-Oszillatorfamilien verfügbar. Die HCSL-Ausgangsstruktur (siehe Abbildung 16, Abbildung 14) wird von einer geschalteten 14-mA-Stromquelle angetrieben, die typischerweise über einen 50-Ω-Widerstand mit Masse verbunden ist, wie in Abbildung 15 dargestellt. Der nominale Signalhub beträgt 700 mV. Der Open-Drain-Transistor am Ausgang hat eine relativ hohe Impedanz im Bereich von mehreren Kiloohm. Aus AC-Sicht liegt die Impedanz des Ausgangstransistors parallel zum 50-Ω-Lastwiderstand, was zu einem Ersatzwiderstand von sehr nahe bei 50 Ω führt. Da die in dieser Schnittstelle verwendeten Leiterbahnen eine charakteristische Impedanz von 50 Ω haben, wird jedes von der Last reflektierte Signal an der Quelle absorbiert. Typischerweise werden zwei kleine Widerstände, R1 und R2 (siehe Abbildung 15), in Reihe mit dem Hochimpedanztreiber geschaltet. Sie fungieren als Überschwingungsbegrenzer, indem sie den schnellen Anstieg des Stroms vom Ausgang verlangsamen und haben keinen Einfluss auf die Impedanzanpassung an der Quelle. SiTime empfiehlt für diese Widerstände 33 Ω.

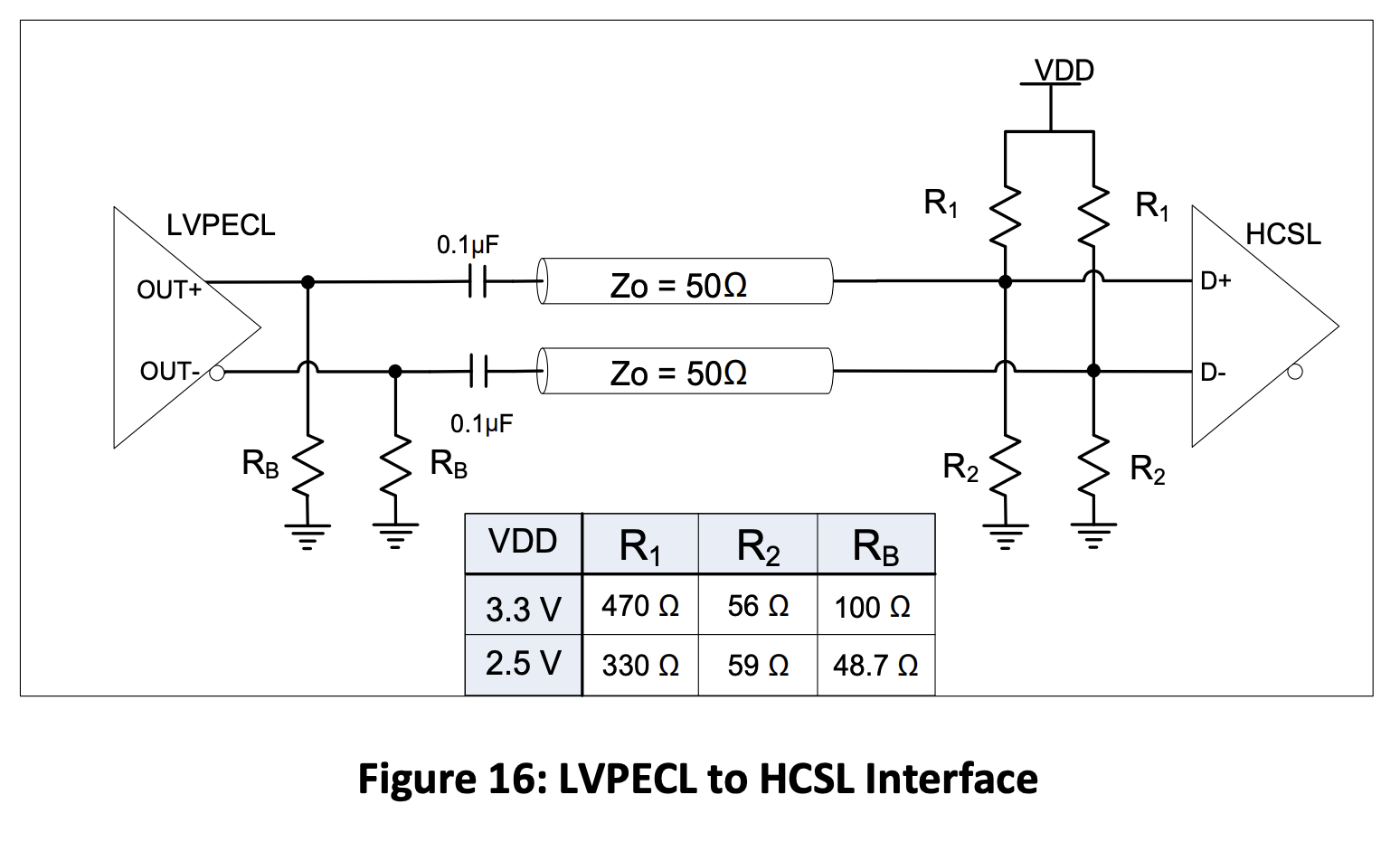

5. Ansteuerung eines HCSL-Empfängers mit LVPECL-Oszillatoren

Eine typische HCSL-Schnittstelle nutzt einen Strommodustreiber und verwendet 50-Ω-zu-GND-Anschlüsse an der Quelle und keinen Abschluss an der Empfängerseite. Zusätzlich zu einem HCSL-Ausgangstreiber kann ein LVPECL-Treiber zum Ansteuern eines HCSL-Eingangs verwendet werden. Abbildung 16 zeigt ein empfohlenes Abschlussschema für die Ansteuerung eines HCSL-Empfängers mit LVPECL-Ausgang. Um den vom HCSL-Empfänger geforderten VOH-Pegel von 750 mV und VOL-Pegel von 0 V zu erfüllen, verfügt er über AC-Kopplungskondensatoren zur Trennung von Quellen- und Lastvorspannungen.

Der gleichwertige Abschluss auf der Lastseite stellt auch die richtige Gleichtaktspannung an den Empfängereingängen ein. Der Widerstand RB sorgt für die richtige Gleichstromvorspannung des LVPECL-Treibers. Die empfohlenen Werte der Abschlussnetzwerkkomponenten sind in Abbildung 16 für Betriebsspannungen von 2,5 V und 3,3 V angegeben.

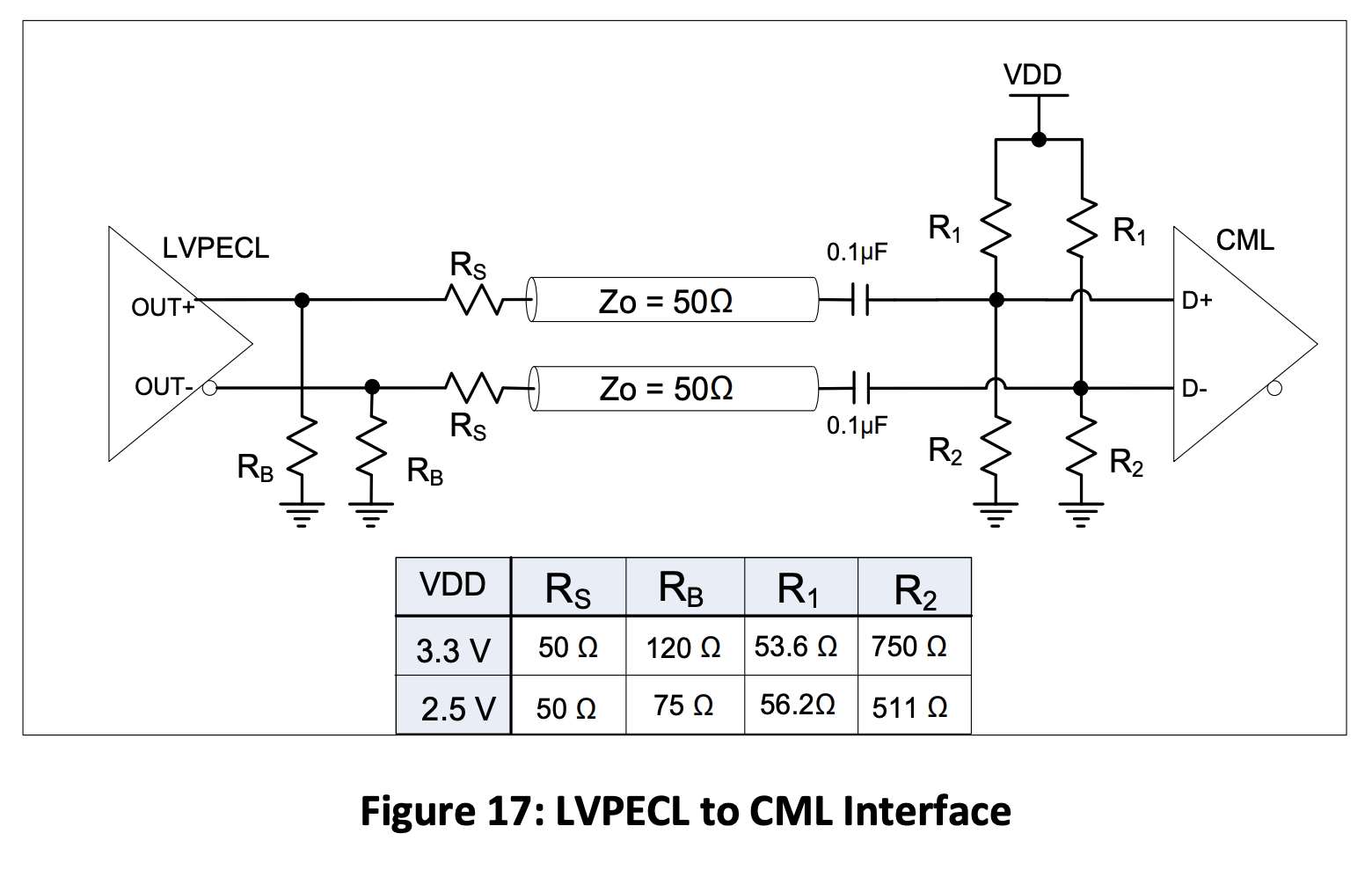

6. Ansteuerung eines CML-Empfängers mit LVPECL-Oszillatoren

Die meisten SiTime-Differenzialoszillatoren verfügen nicht über eine CML-Ausgangsoption, können aber mithilfe eines LVPECL-Treibers zum Ansteuern eines CML-Empfängers verwendet werden. In diesem Fall muss das Abschlussschema 400 mV Single-Ended-Spannungsschwankungen an den Empfängereingängen und VDD – 200 mV Gleichtaktspannung gewährleisten [2]. Abbildung 17 zeigt ein empfohlenes Abschlussschema für die Ansteuerung eines CML-Empfängers mit LVPECL-Ausgang. Aufgrund des großen Unterschieds zwischen LVPECL- und CML-Gleichtaktspannungen sind AC-Kopplungskondensatoren zur Gleichstromisolierung erforderlich. Der Widerstand RB wird für die ordnungsgemäße Vorspannung des LVPECL-Treibers verwendet. Der gleichwertige Abschluss auf der Empfängerseite stellt die richtige Vorspannung ein und sorgt zusammen mit dem RB-Widerstand für den richtigen Signalhub.

7. Ansteuerung selbstvoreingenommener Differenzeingänge

Viele Differenzempfänger verfügen über On-Chip-DC-Bias-Schaltkreise und/oder Abschlussnetzwerke. In diesem Fall sollten die Oszillatorausgänge wechselstromgekoppelt sein. Wenn eine externe Vorspannung erforderlich ist, sollte diese gemäß dem Datenblatt des Empfängergeräts ausgelegt werden.

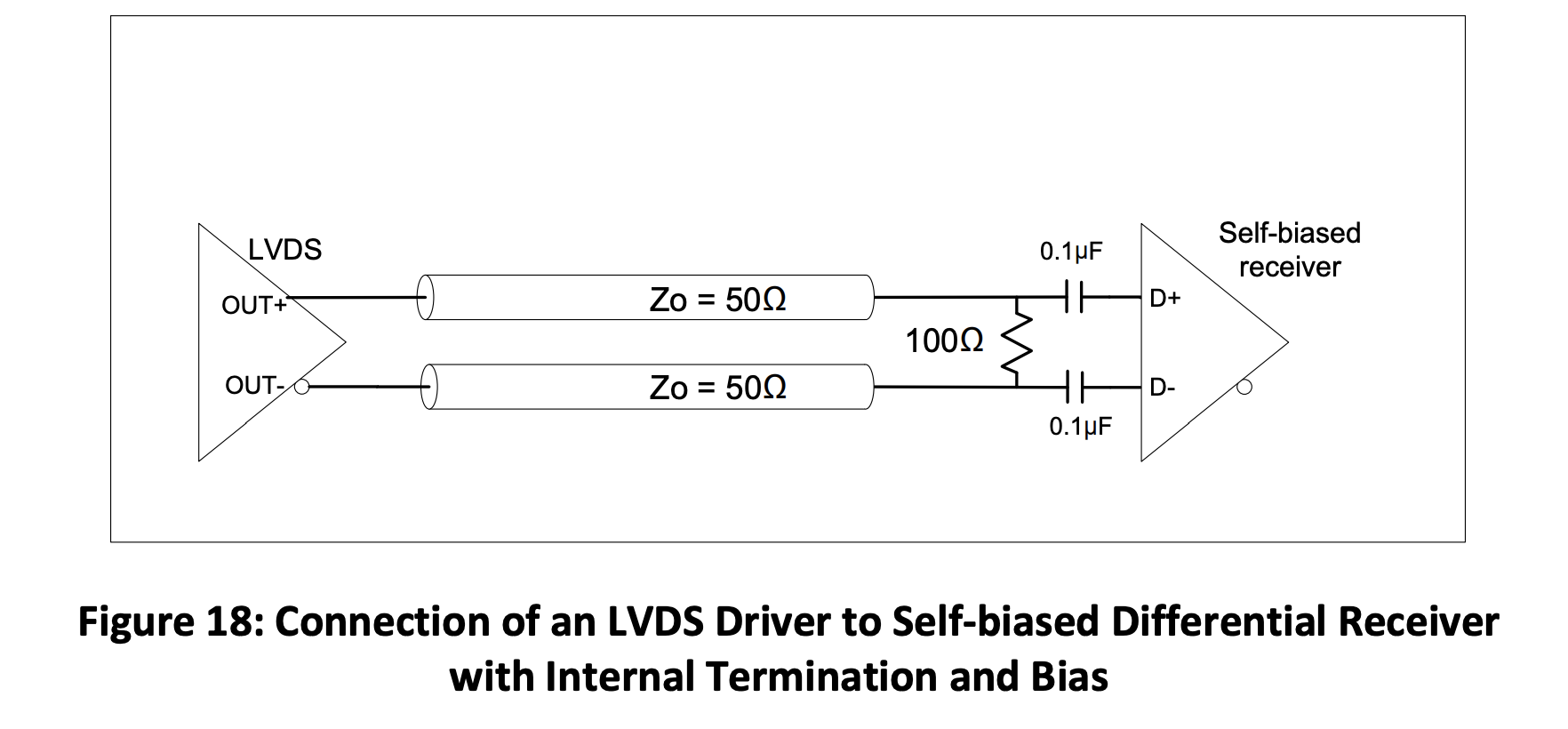

LVDS- oder LVPECL-Oszillatoren können zur Ansteuerung selbstvorgespannter Differenzeingänge verwendet werden. Der LVDS-Ausgang erfordert weniger passive Komponenten und eine geringere Betriebsleistung. Wenn 700 mV LVDS-Schwingung für den Empfänger ausreichen, ist die Verwendung eines LVDS-Oszillators vorzuziehen. Abbildung 18 zeigt die Verbindung eines LVDS-Oszillators mit einem selbstvorgespannten Differentialempfänger.

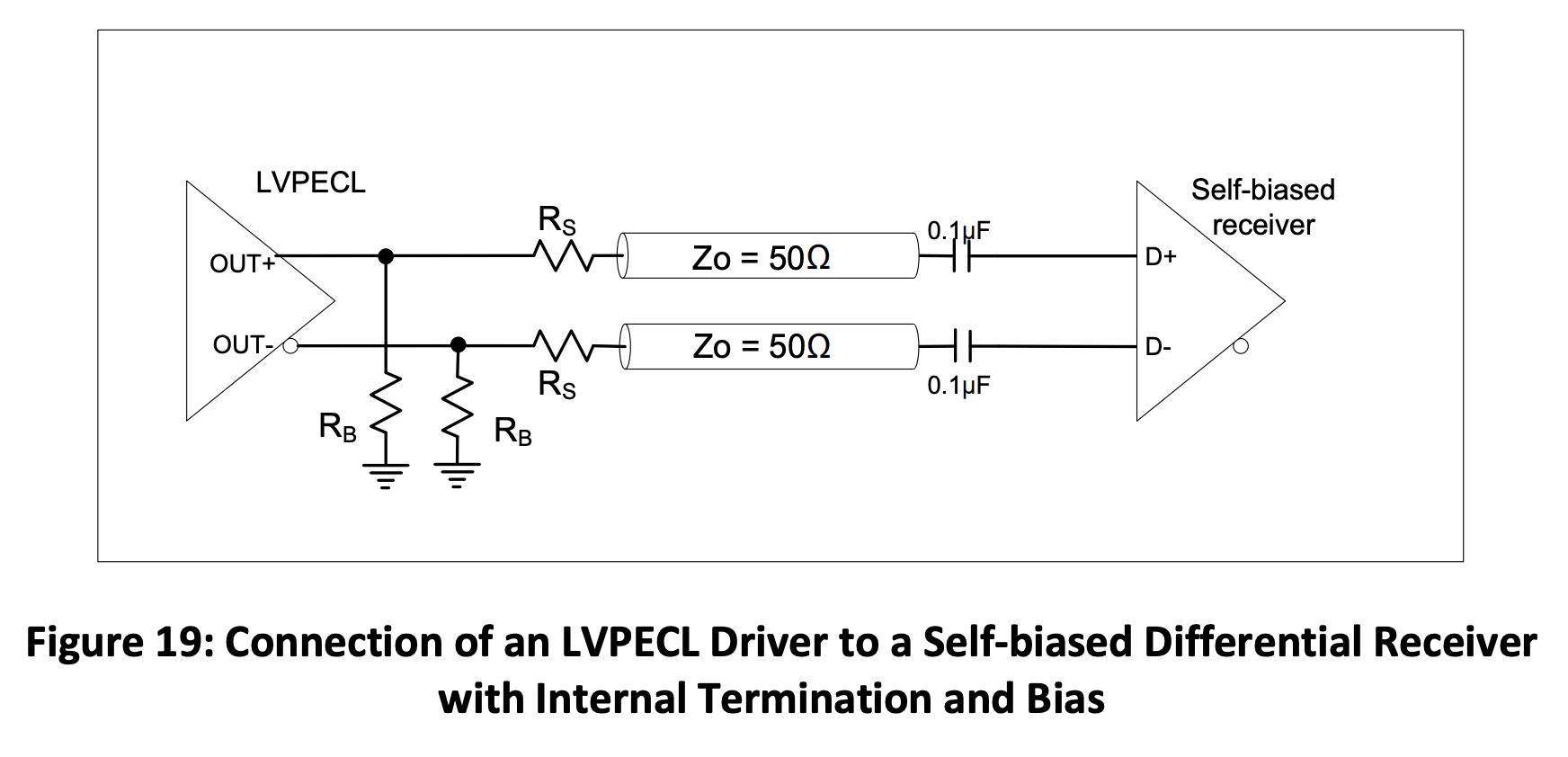

Der LVPECL-Ausgang kann am Empfänger einen Differenzhub von bis zu 1,6 V erzeugen. Abbildung 19 zeigt ein Schema für den Anschluss eines LVPECL-Oszillators an einen selbstvorgespannten Differentialempfänger. Der Widerstand RS bildet einen Spannungsteiler mit lastseitigem Abschluss. Der Spannungshub am Empfängereingang kann durch Auswahl des RS-Werts eingestellt werden. RB liefert Gleichstrom-Vorstrom für den LVPECL-Treiber und sein Wert kann aus Gleichung 1 berechnet werden. Bitte beachten Sie, dass der Empfänger einen effektiven Abschlusswiderstandswert von RS + 50 Ω sieht.

Um die Signalintegrität aufrechtzuerhalten, sollten RS und RB so nah wie möglich am Oszillator vor der Übertragungsleitung platziert werden. Das lastseitige Abschlussnetzwerk sollte so nah wie möglich an den Empfängereingängen platziert werden.

8. Ansteuerung eines LVDS-Empfängers mit einem LVPECL-Treiber

Ein LVDS-Empfänger kann mit einem LVPECL-Taktsignal angesteuert werden. Dies erfordert den Einsatz von Abschlusstechniken, die das Signal auf der Empfängerseite in die LVDS-Signalisierungsanforderungen bringen. Die wichtigsten Spezifikationen, die eingehalten werden müssen, sind die Gleichtaktspannung und die Signalamplitude des Signals. Um die LVDS-Spezifikationen zu erfüllen, muss die LVPECL-Signalamplitude von 1,6 V auf 0,75 V reduziert werden. Die Gleichtaktspannung des LVPECL-Treibers hängt von der Versorgungsspannung ab und entspricht bei 2,5 V VDD der LVDS-Gleichtaktspannung. Der Abschluss, der das Takten eines LVDS-Empfängers mit einem 2,5-V-LVPECL-Treiber ermöglicht, ist in Abbildung 20 dargestellt.

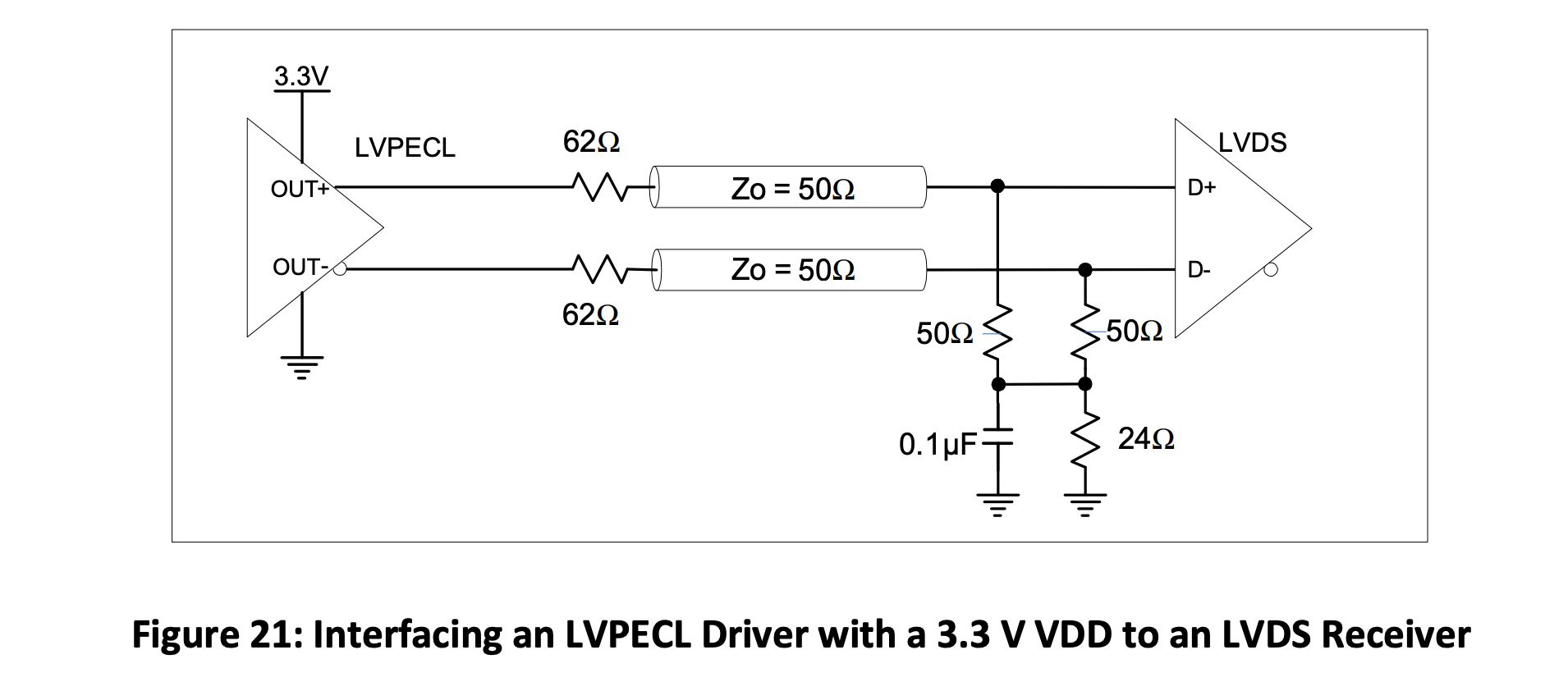

Bei 3,3 V VDD sind die Gleichtaktspannungen des LVPECL-Treibers und des LVDS-Empfängers unterschiedlich. Abbildung 21 schlägt die Verwendung von Vorwiderständen und einem Y-Abschluss als Schnittstelle zwischen einem LVPECL-Treiber und einem LVDS-Empfänger vor.

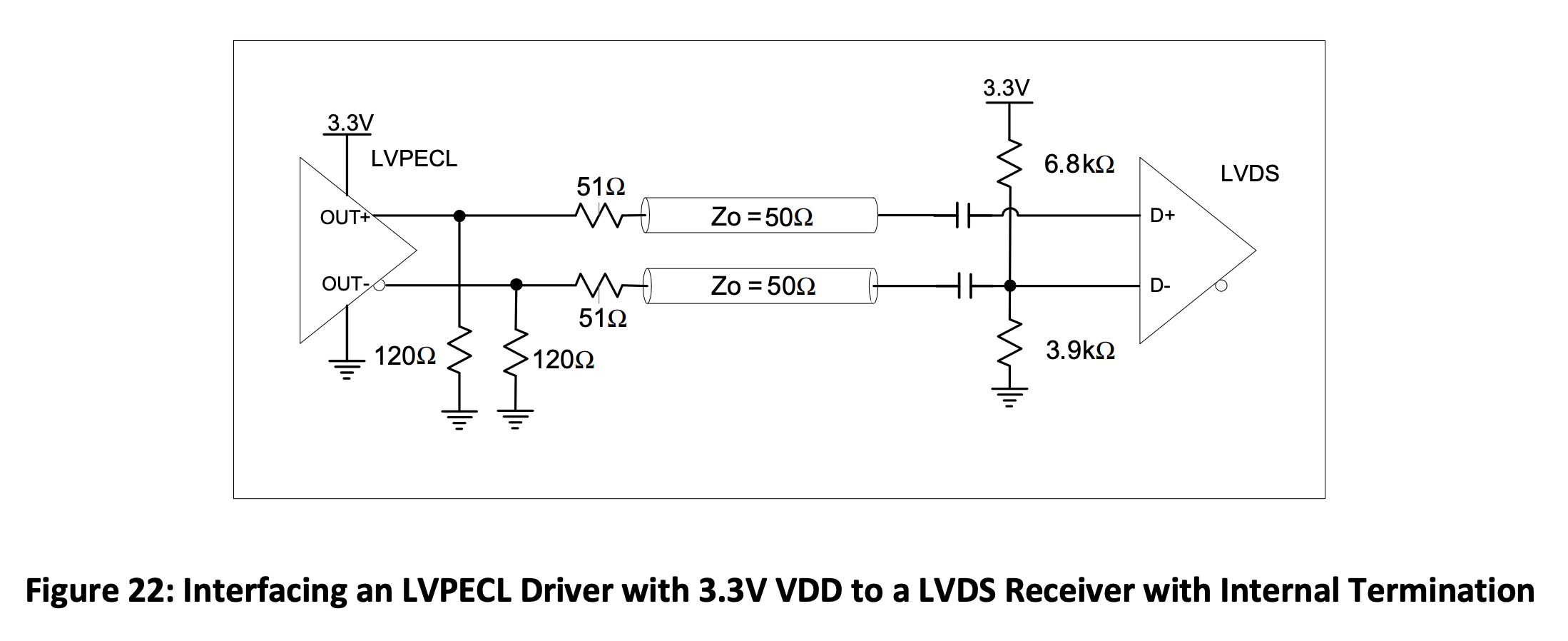

Wenn der Empfänger über einen On-Chip-Abschluss verfügt, wird eine Wechselstromkopplung empfohlen, wie in Abbildung 22 dargestellt. Der Gleichtakt wird durch einen Widerstandsteiler eingestellt. Da sein äquivalenter Widerstand zu hoch ist, um ein Ungleichgewicht zwischen positiven und negativen Eingängen zu verursachen, ist nur einer der Eingänge vorgespannt.

9. Anbindung eines LVCMOS-Oszillators an einen LVDS/LVPECL-Eingang

In einigen Fällen sind taktende differenzielle LVDS- oder LVPECL-Empfänger mit einer Single-Ended-Ausgangsquelle erforderlich. Der LVCMOS-Ausgang kann an einen LVDS- oder LVPECL-Empfänger angeschlossen werden, indem ein AC-Signal an einen der Differenzeingangspins angeschlossen und eine DC-Schwellenspannung an den anderen Pin angelegt wird. Um die Anforderungen an den Differenzhub zu erfüllen, muss die Amplitude eines Single-Ended-Takts auf der Empfängerseite doppelt so hoch sein wie der Differenzhub einer LVDS- oder LVPECL-Schnittstelle. Sehen Sie im Datenblatt des Empfängers nach, um sicherzustellen, dass die Eingangsspannung innerhalb akzeptabler Grenzen liegt.

Die Ansteuerung des LVDS/LVPECL-Eingangs mit einem Single-Ended-Oszillator bietet im Vergleich zu einem Differentialoszillator einen viel geringeren Stromverbrauch, verringert jedoch die Störfestigkeit.

Die Anbindung eines Single-Ended-Ausgangs an einen Differenzempfänger erfordert die folgenden Bedingungen:

- Die Gleichtaktspannung an den Eingängen sollte 1,2 V für LVDS bei allen VDDs, 1,2 V für LVPECL bei 2,5 V VDD und 2 V für LVPECL bei 3,3 V VDD betragen.

- Der Spannungshub an den Eingängen sollte 700 mV bis 800 mV für LVDS und 1,2 V bis 2 V für LVPECL betragen.

- Die Eingangsimpedanz des Abschlussschaltkreises muss mit der Leiterbahnimpedanz übereinstimmen, um die Signalintegrität aufrechtzuerhalten. Die typische Leiterbahnimpedanz beträgt 50 Ω.

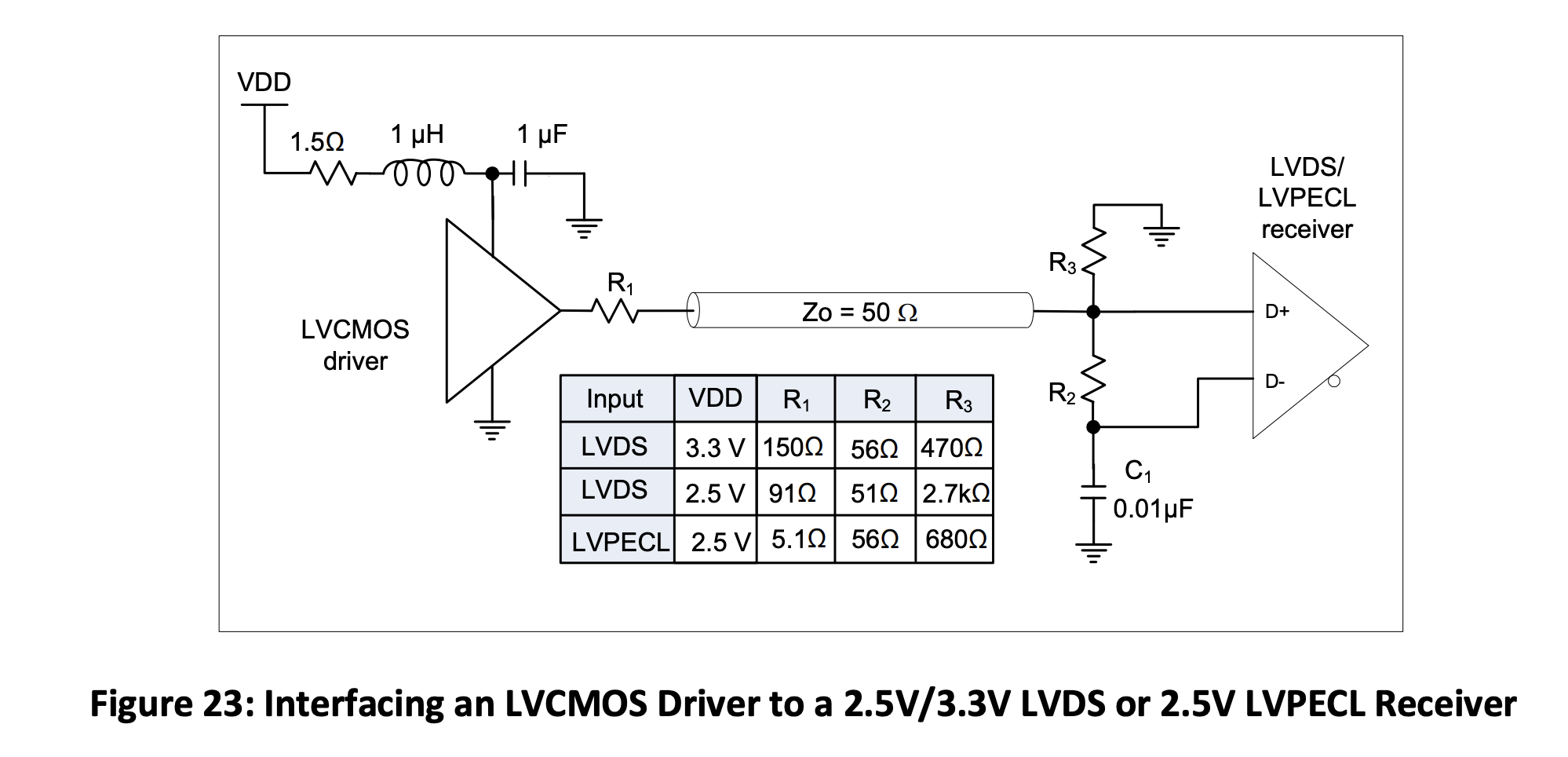

Abbildung 23 zeigt ein empfohlenes Schema für die Anbindung eines Single-Ended-Ausgangs an beliebige Spannungs-LVDS und LVPECL bei 2,5 V VDD. Die Gleichtaktspannung wird durch einen Spannungsteiler eingestellt, der aus der Ausgangstreiberimpedanz und den Widerständen R1 und R3 besteht. Der Kondensator C1 stellt einen Wechselstromsignalpfad vom negativen Eingang zur Masse bereit. Die Signalamplitude am positiven Eingang wird durch den Spannungsteiler eingestellt, der aus einem Ausgangstreiberwiderstand in Reihe mit R1 und R2 parallel zu R3 besteht.

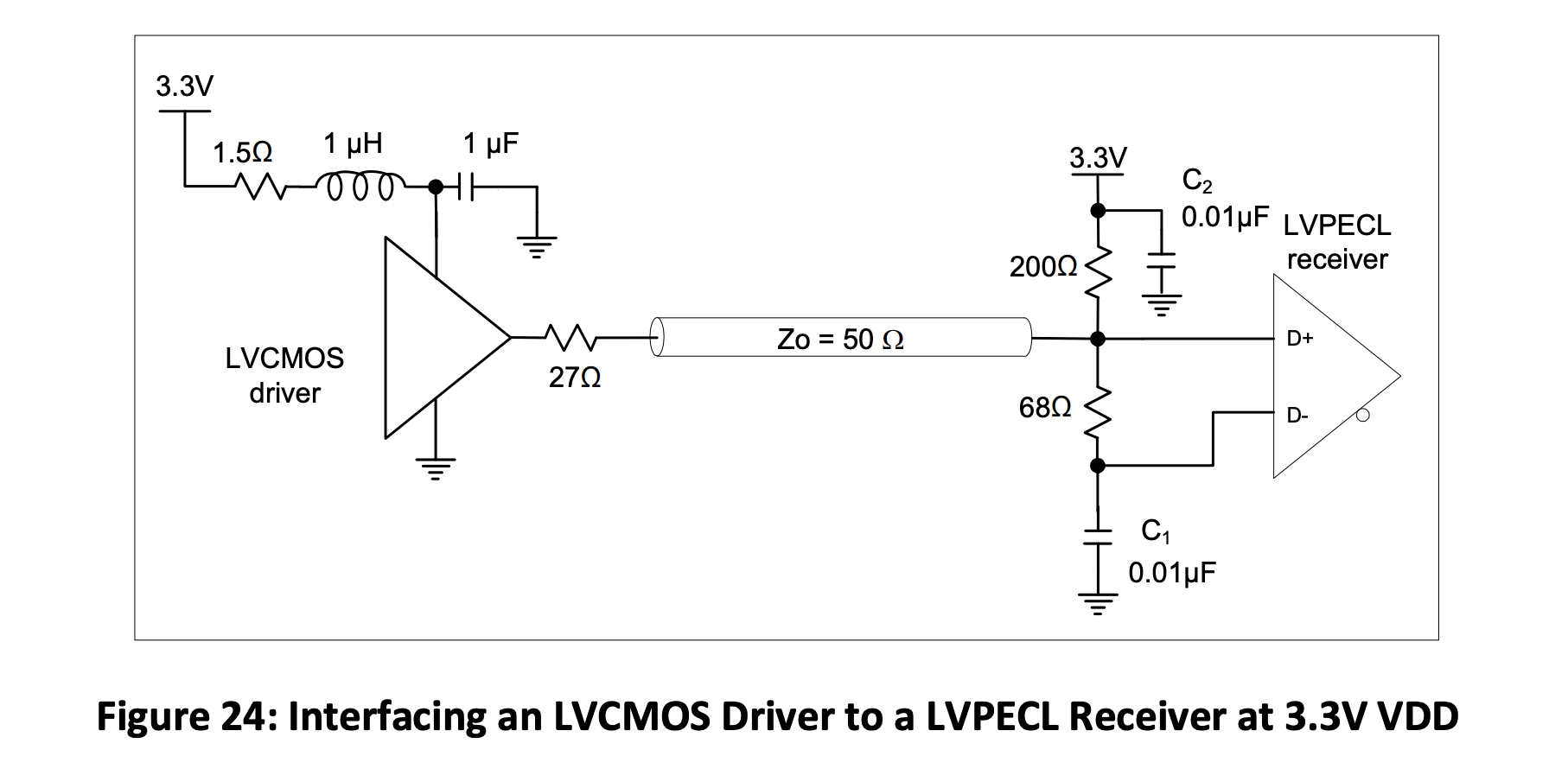

Abbildung 24 zeigt ein Schema für die Verbindung von LVCMOS zu LVPECL bei 3,3 V VDD. Die Gleichtaktspannung auf der Empfängerseite wird durch einen Spannungsteiler eingestellt, der durch eine Ausgangstreiberimpedanz in Reihe mit einem 27-Ω-Widerstand und einem 200-Ω-Pullup an VDD erzeugt wird.

Die empfohlenen Komponentenwerte in Abbildung 23 und Abbildung 24 werden auf der Grundlage einer LVCMOS-Treiberimpedanz von 25 Ω berechnet. Dieser Wert entspricht der typischen Treiberimpedanz der LVCMOS-Oszillatoren der Familie SiT8008.

Der LVCMOS-Oszillator verfügt in seinem Stromversorgungsnetzwerk über einen RLC-Filter (siehe Abbildung 23 und Abbildung 24). SiTime empfiehlt die Verwendung dieses RLC-Filters, da er die Rauschunterdrückung der Stromversorgung erheblich verbessert.

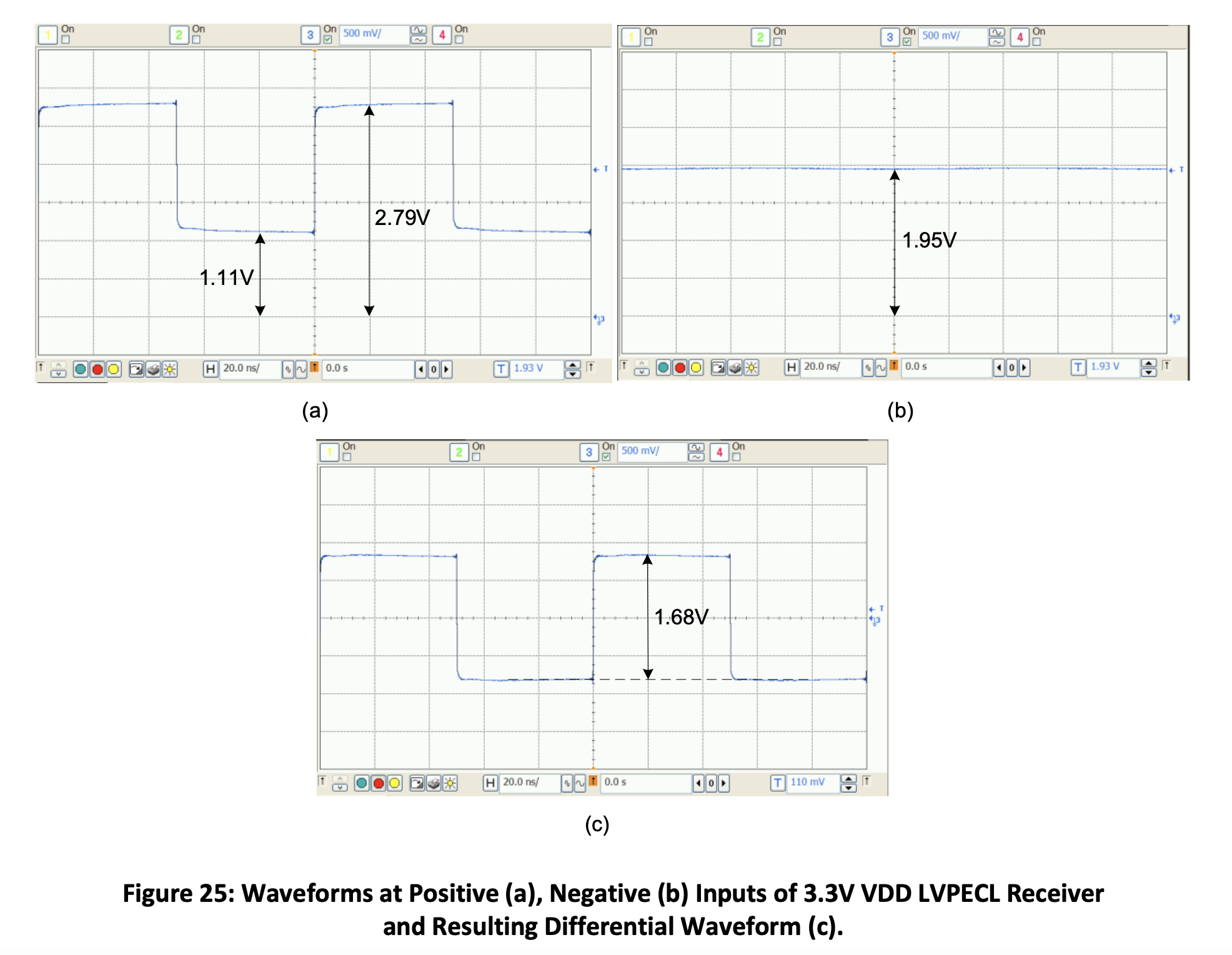

Abbildung 25 zeigt Beispiele für Wellenformen an den Eingängen des 3,3-V-LVPECL-Empfängers bei Ansteuerung mit einem Single-Ended-Takt.

10. Fazit

In diesem Anwendungshinweis werden die Ausgangstreiberstrukturen für SiTime-Differenzoszillatoren und die am häufigsten verwendeten AC-gekoppelten und DC-gekoppelten Abschlussschemata für LVPECL-, LVDS- und HCSL-Differenzausgänge vorgestellt. Empfohlene Optionen für die Anbindung an HCSL- und CML-Empfänger mit LVPECL-Ausgang werden besprochen. Es werden auch Abschlussschemata vorgestellt, die die Ansteuerung eines LVDS- oder LVPECL-Taktempfängers mithilfe eines Single-Ended-LVCMOS-Oszillators ermöglichen. Mit einer großen Auswahl an Ausgangstypen können Benutzer ein Ausgangssignal auswählen, das ihren Anforderungen am besten entspricht.

Wenn Sie ein PDF dieser Anwendungsnotiz [AN10029] herunterladen möchten, klicken Sie hier . Anhang A ist im PDF enthalten.

Revisionsverlaufstabelle

Ausführung | Veröffentlichungsdatum | Zusammenfassung ändern |

1,0 | 30.04.20013 | Originaldokument. |

2,0 | 01.11.2013 | Änderungen zur Verdeutlichung. Abschnitt hinzugefügt: Ansteuerung eines LVDS-Empfängers mit einem LVPECL-Laufwerk Abschnitt hinzugefügt: Anbindung eines LVCMOS-Oszillators an einen LVDS/LVPECL-Eingang |

2.1 | 19.06.2018 | Das Dokument wurde neu strukturiert und ein neues Seitenlayout mit aktualisiertem Logo und neuer Firmenadresse angewendet. Änderungen zur Verdeutlichung. Abschnitt 4: HCSL-Ausgabe hinzugefügt. Die Liste der SiTime-Oszillatoren wurde aktualisiert, um die aktuelle Produktlinie widerzuspiegeln, und in Tabelle 1 verschoben. |