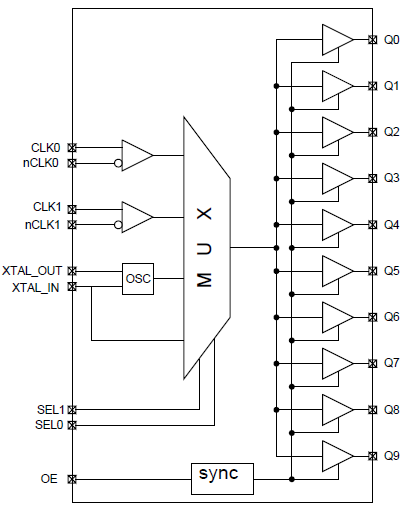

Der SiT92110 ist ein Fanout- Taktgeber mit 10 Ausgängen und geringem Jitter. Er ist ideal für die jitterarme, hochfrequente Taktgeber/Datenverteilung. Die LVCMOS-Ausgänge mit niedriger Impedanz sind für die Ansteuerung von seriell oder parallel geschalteten 50-Ω-Übertragungsleitungen ausgelegt.

Der Puffer kann einen Taktgeber von primären oder sekundären Taktgeber verwenden, entweder unsymmetrisch oder volldifferenziell. Der ausgewählte Taktgeber wird an 10 LVCMOS-Ausgangstreiber verteilt.

Der SiT92110 wird mit einer Kernversorgung von 3,3 V/2,5 V/1,8 V und einer Ausgangsversorgung von 3,3 V/2,5 V/1,8 V/1,5 V betrieben. Die Kernversorgung und die Ausgangsversorgung sind voneinander unabhängig und es ist keine Versorgungssequenzierung erforderlich.

| "Spezifikationen" | "Wert" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 5x5 mm, 32-pin QFN |

| Buffer Type | Fanout |

| Number of Inputs | 1 |

| Number of Outputs | 10 Single Ended |

| Input Type | LVPECL, LVDS, LVCMOS, SSTL, HCSL |

| Input Frequency Range | 0 Hz to 250 MHz |

| Output Type | LVCMOS |

| Output Frequency Range | 0 Hz to 250 MHz |

| Additive Phase Jitter (rms) | 50 fs |

| Propagation Delay, Typical | 1.4 ns |

| Output-Output Skew, Typical | 30 ps |

| Availability | Production |

-

5x5 mm, 32-pin QFN Clock Buffer package

- Pegelumsetzung mit Kernversorgungsspannung von 3,3 V/2,5 V/1,8 V und 3,3 V/2,5 V/1,8 V/1,5 V Ausgangsversorgung für LVCMOS-Ausgangstreiber.

- Die Eingänge werden durch Programmieren der Eingangsauswahlpins von SiT92110 ausgewählt. Der Taktgeber in SiT92110 kann LVPECL-, LVDS-, LVCMOS-, SSTL-, HCSL- und OSC-Wellenformen akzeptieren.

SiT92110 Evaluation Board HW Benutzerhandbuch – Baustein konfigurieren und bewerten

| Resource Name | Resource Type | Date | Format | Size |

|---|