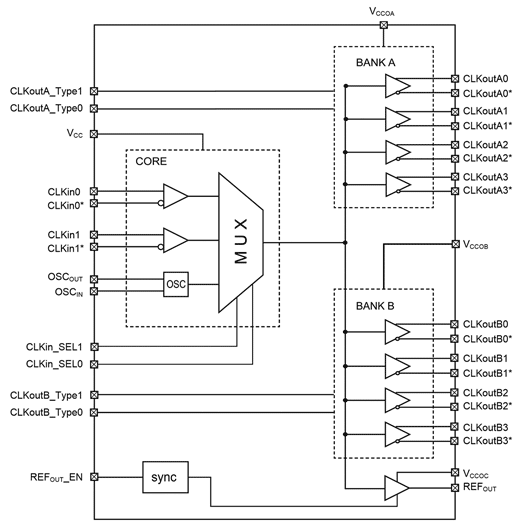

SiT92208 是一款 8 输出、低抖动扇出时钟缓冲器,支持高达 2.1 GHz 的频率。它是低抖动、高频时钟/数据分配和电平转换应用的理想选择。

缓冲器可使用来自主时钟源或次时钟源的时钟输入,可以是单端时钟源,也可以是全差分时钟源。所选时钟可分配至两个输出驱动器组 A、B 和一个 LVCMOS 输出。

每个组的输出驱动器均可独立编程为 LVPECL、LVDS、HCSL 或 HIZ 模式。LVCMOS 时钟输出与所选时钟同步,并可无故障地启用或禁用。

SiT92208 采用 3.3 V/2.5 V 核心电源和 3 个独立的 3.3 V/2.5 V 输出电源供电。LVCMOS 输出驱动器可在 1.8 V 下工作。

| "眼镜" | "值" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 6x6 mm, 40-pin QFN |

| Buffer Type | Fanout |

| Number of Inputs | 3 |

| Number of Outputs | 8 Differential |

| Input Type | LVPECL, LVDS, LVCMOS, SSTL, HCSL |

| Input Frequency Range | 0 Hz to 2.1 GHz |

| Output Type | LVPECL, LVDS, HCSL, LVCMOS |

| Output Frequency Range | 0 Hz to 2.1 GHz |

| Additive Phase Jitter (rms) | 55 fs (typ.) |

| Propagation Delay, Typical | 1.4 ns |

| Output-Output Skew, Typical | 30 ps |

| Availability | Sampling |

-

6x6 mm, 40-pin QFN Clock Buffer package

- 3:1 输入时钟选择。

- 两个通用时钟输入最高可运行 2.1 GHz,并接受 LVPECL、LVDS、LVCMOS、CML(仅交流耦合)、HCSL、SSTL 或单端时钟。

- 两个输出驱动器组 A 和 B,可独立编程为 LVPECL、LVDS、HCSL 或 HIZ 模式。

- 具有 3.3 V/2.5 V 核心电源电压和 3.3 V/2.5 V 输出电源的电平转换,适用于差分输出驱动器。

- 单个 LVCMOS 输出驱动器的电压为 3.3 V/2.5 V/1.8 V。

- LVPECL/LVDS 模式的高 PSRR 为 -70/-73 dBc。

- 支持 PCI-e Gen 1 至 Gen 5。

Apply Filters

| Resource Name | Resource Type | Date | Format | Size |

|---|