Why the JEDEC JESD204 Standard Is Gaining Traction—JESD204B Subclasses and What You Need to Know

In the dynamic world of high-speed data communications, the JEDEC JESD204 standard is a cornerstone for efficient data transmission between high-speed analog-to-digital and digital-to-analog data converters (ADCs and DACs) and logic devices such as FPGAs, ASICs and DSPs. The JESD204 standard defines a serial interface that reduces board space, improves speed and lowers cost compared to more conventional interfaces. The initial version of the standard, JESD204, reduces the number of data inputs into DACs and the number of data outputs out of ADCs. It streamlines data transmission between the converters and the transceiver (Tx) and receiver (Rx) component parts. Since the JESD204 standard was first introduced, it has evolved with new generations, adding groundbreaking features to keep pace with the introduction of high-speed converters and logic devices. This overview covers the JESD204 A/B/C evolution, including the importance of the subclasses that were first introduced with JESD204B.

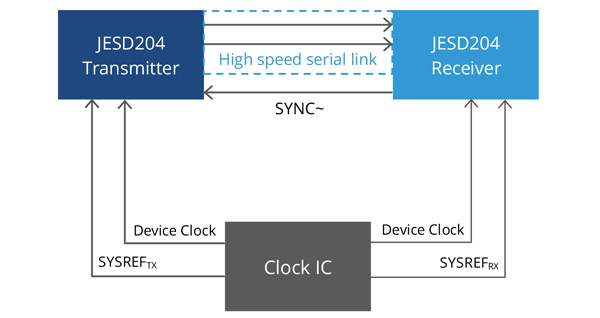

Figure 1. High-level block diagram showing a JESD204 interface between an ADC Tx and an FPGA Rx.

Overview of the JESD204 Evolution

Originally conceived to simplify the design complexities in high-speed data converters, the JESD204 standard has evolved significantly. The standard is poised to dominate electronic system design as the favored solution for data conversion and transmission.

JESD204:

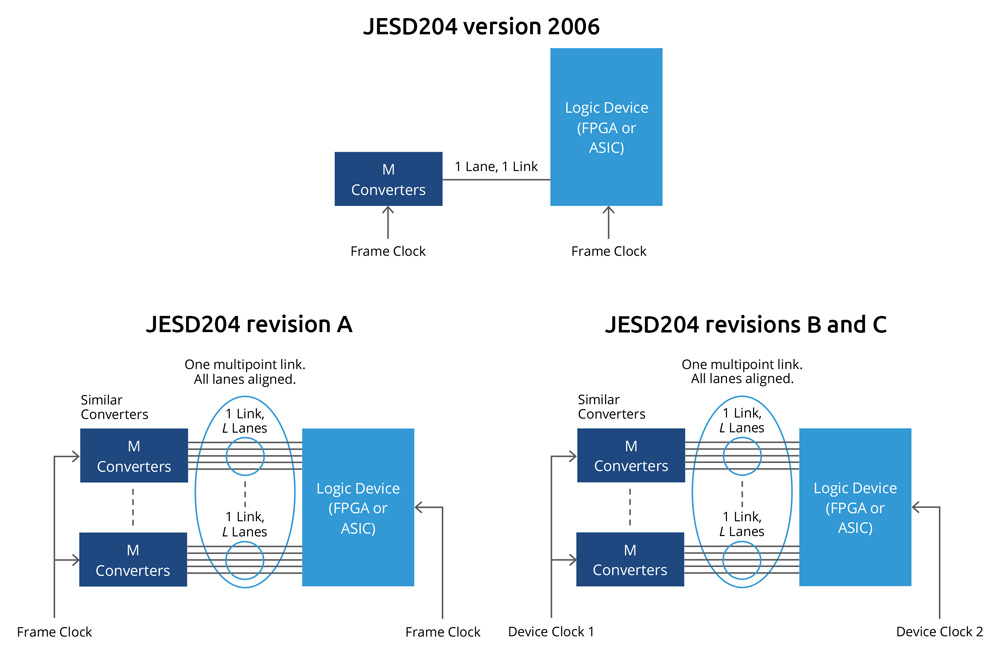

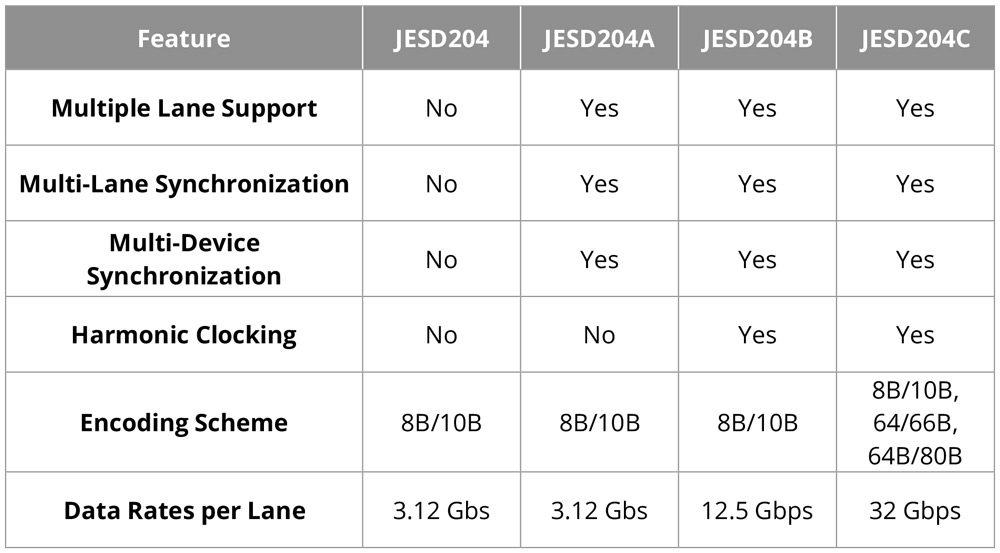

JESD204 was the first version of the standard and introduced in 2006, enabling enhancements in data transmission speed and bandwidth to facilitate higher throughput. While the data rate was 3.12 Gbps, JESD204 had limitations in synchronizing data between multiple converters and devices.

JESD204A:

The JESD204A version was introduced in 2008. It differed from its predecessor by providing multi-lane support at 3.12 Gbps per lane, as well as multi-lane synchronization and multi-device synchronization, addressing JESD204 limitations.

JESD204B:

JESD204B, introduced in 2011, added groundbreaking subclasses, lending greater flexibility in multi-device synchronization, most notably introducing deterministic latency. It is also four times faster and enables harmonic clocking. This iteration brought substantial improvements for designs, including:

Increased Data Rates—JESD204B addressed the burgeoning need for speed in applications such as wireless 5G front-haul networks, radar systems, satellite communications, and digital imaging by enabling faster data transmission up to 12.5 Gbps per lane.

Introduction of Subclasses—To tackle synchronization issues at higher speeds, JESD204B introduced subclasses. Each subclass enables different levels of synchronization between data converters and other system components. This marks a transformative moment in high-speed data systems, significantly influencing how data converters synchronize, impacting system performance, design and efficiency.

- Subclass 0, basic functionality: This subclass offers basic functionality without specific provisions for synchronization. It is suitable for systems where synchronization is not a critical factor.

- Subclass 1, deterministic latency using SYSREF: Subclass 1 enables synchronization between data converter and device clock domains. It uses a system reference signal (SYSREF) to align the internal clocks of converters, ensuring better synchronization. SYSREF has been a game-changer, ensuring that all data converters in a system are aligned to a common clock signal, minimizing timing errors and improving data integrity. The impact is profound in systems requiring tight synchronization, such as phased array radars, radio units or multi-channel audio systems.

- Subclass 2, precise timing control and deterministic latency using SYNC~: This is the most advanced JESD204B subclass. It guarantees that the conversion process across multiple devices starts at precisely the same system clock cycle. This level of precision is important for applications such as 5G Multiple Input Multiple Output (MIMO) systems in wireless communication, where timing discrepancies can significantly affect performance.

Table 1. Differences between the three subclasses of JESD204B.

JESD204C:

The introduction of JESD204C in 2017 significantly improved serial data rates. At 32 Gbps, it is over 2.5X faster than JESD204B. In addition to an 8B/10B link layer like the previous version, it also has 64/66B and 64B/80B link layers for clock recovery and receiver training and equalization with reduced overhead.

Figure 2. Three block diagrams depicting the original JESD204 standard and revisions A, B and C. (Source: JEDEC Standard, Serial Interface for Data Converters, JESD204C, Revision of JESD204B.01 January 2012.)

Table 2. Summary of the different versions of JESD204.

Why JESD204B Subclasses Are a Big Deal: Enhanced Synchronization, Timing Accuracy and Streamlining System Design

Subclasses, first introduced with JESD204B, was a breakthrough for the standard. Some of the many benefits of the subclasses include:

- Simplifying configurations to reduce system complexity: Subclasses simplify the design of complex systems by standardizing synchronization processes. This reduces the need for custom solutions, allowing system designers to focus on other aspects of system optimization.

- Design flexibility: By offering different levels of synchronization control, the subclasses allow designers to choose the most appropriate subclass for their specific application, providing a balance between system complexity and synchronization needs.

- Integration and scalability: The standardization brought by subclasses has made it easier to integrate multiple data converters and scale systems up or down, depending on the application's requirements.

- Improving data integrity and noise reduction: Accurate synchronization minimizes the risk of data corruption. In high-speed data systems, even minor timing discrepancies can lead to significant data errors. The subclasses help maintain data integrity, especially in systems where large volumes of data are transmitted at high speeds. Synchronization reduces system noise, a critical factor in applications such as medical imaging or high-precision instrumentation. By aligning the timing of data converters, subclasses reduce the likelihood of noise-induced errors, enhancing the overall quality of data.

Before the advent of JESD204B subclasses, designers often faced challenges in managing multiple interfaces between data converters and other components. The subclasses have streamlined this process to reduce the interface complexity and enhance system reliability.

Future Proofing Designs by Adopting JESD204C and Beyond

As technology evolves, so do the requirements for high-speed data systems. The JESD204B subclasses provide a framework that is adaptable, helping ensure that systems can keep pace with emerging technologies. From enhancing synchronization and timing accuracy to streamlining system design and ensuring data integrity, these subclasses are integral to modern electronic system design. They highlight the dynamic nature of technology and the constant need for innovation in high-speed data communication. Subclasses help ensure backward compatibility and illustrates JEDECs commitment to evolving with an advancing industry and future proofing the standard.

Related Products

SiTime JESD204-compliant clocks:

Jitter Cleaners

Network Synchronizers

Clock Generators