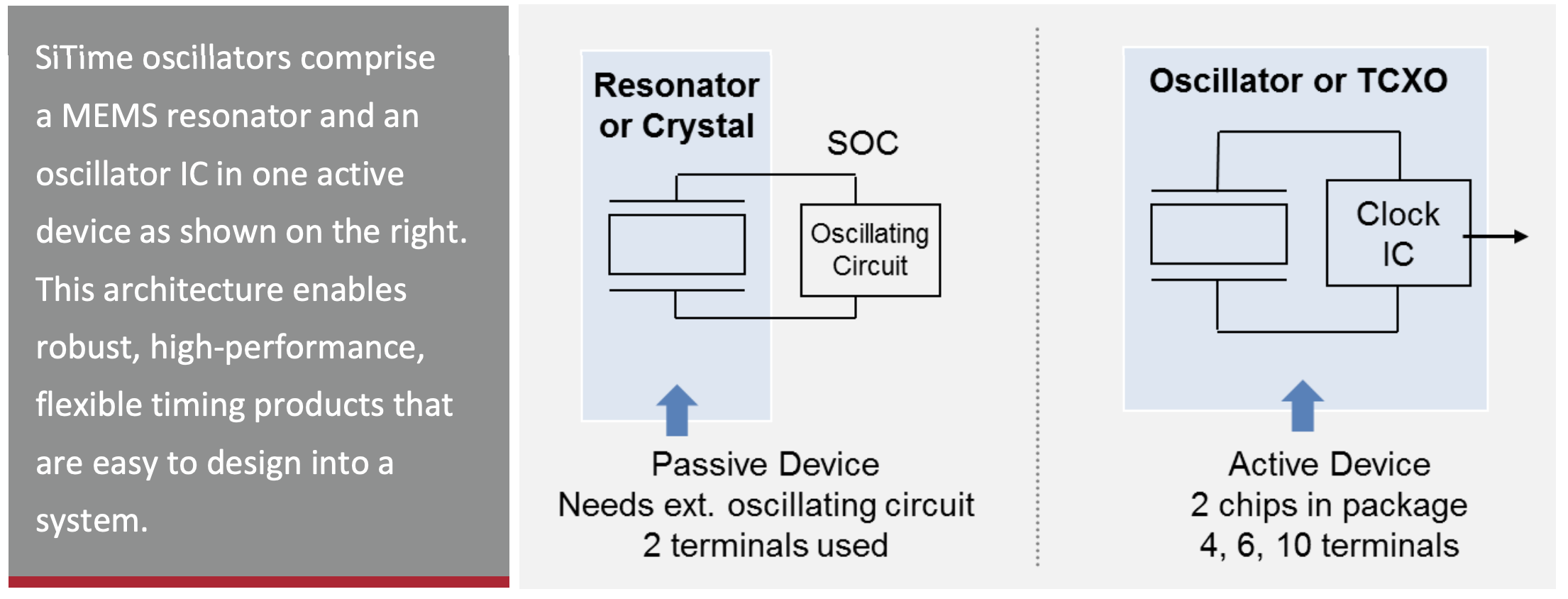

すべての電子システムにはタイミング デバイスが必要です。そして、多くの場合、水晶 (XTAL) 共振器が頼りになるソリューションとなります。ただし、発振器と発振器 IC を組み合わせて 1 つの完全な統合タイミング デバイスを構成する発振器には、XTAL と比較していくつかの利点があります。これらの利点は、 MEMS タイミング技術によってさらに拡張されます。システム設計者は、XTAL の制限を回避したり、クリスタルを使用した設計の頭痛やリスクを受け入れる必要がなくなりました。

1. プラグアンドプレイの発振器によりシステム設計が簡素化されます

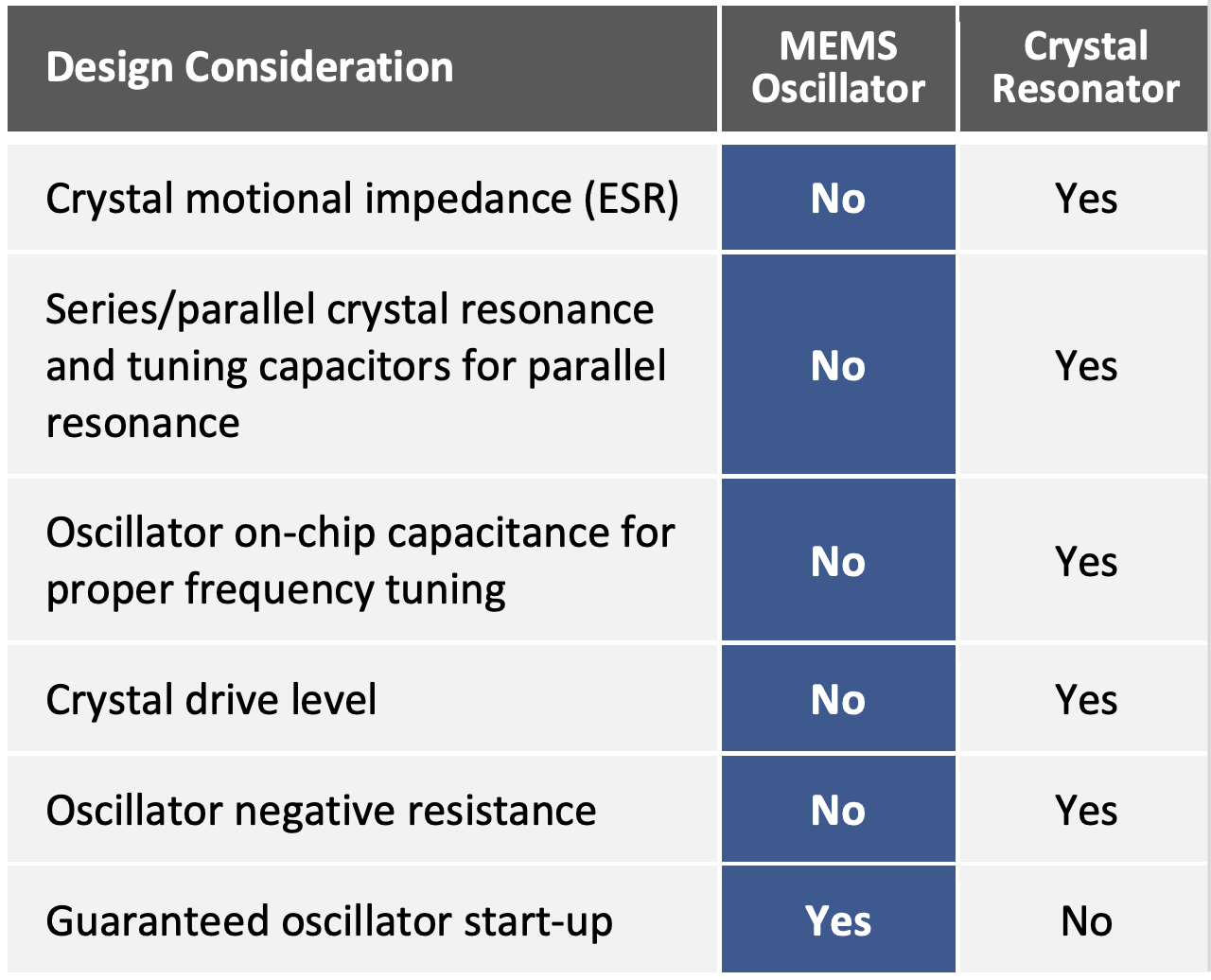

表面上、特にこの技術の成熟度を考慮すると、水晶を使用した発振器の設計は簡単に見えるかもしれません。しかし、水晶を発振回路に適合させる際には、考慮すべき設計パラメータが無数にあります。これらのパラメータには、水晶の動作インピーダンス、共振モード、駆動レベル、および発振器のゲインの尺度である発振器の負性抵抗などがあります。さらに、並列共振モードの水晶では負荷容量を考慮する必要があり、PCB の寄生容量と、発振回路に含まれる可能性のあるオンチップ集積容量を考慮する必要があります。

回路の信頼性の高い起動と動作を保証するには、これらすべてのパラメータを慎重に考慮する必要があります。発振回路では共振器と発振回路の厳密な整合が必要なため、水晶のベンダーは水晶の起動を保証できません。対照的に、オシレーターは完全に統合されたソリューションです。発振器メーカーは水晶振動子を発振器回路に適合させるため、基板設計者のこの負担を軽減します。マッチングエラーが排除されるため、発振器の起動は SiTime によって保証されます。つまり、発振器はシステム設計を大幅に簡素化するプラグアンドプレイのソリューションです。

MEMS発振器で設計上の懸念を解消

水晶の動作インピーダンスと発振器の負性抵抗

発振回路には、バルクハウゼンの発振基準を満たすのに十分なゲインと位相シフトが必要です。特に重要なのは、水晶の動作インピーダンス (ESR) と発振器の負性抵抗 (ゲインに相当) です。発振器のゲインが水晶共振子の動作インピーダンスを克服するには不十分な場合、回路が起動しない可能性があります。これらの問題は、発振器を使用することで解決されます。

水晶共振モード、周波数同調容量、オンチップオシレータ容量

水晶振動子は直列共振モードまたは並列共振モードで共振できますが、通常はこれら 2 つのモードのうちの 1 つに対してのみ校正されます。並列共振用に校正されている場合、通常は指定されている特定の負荷容量が必要です。ただし、適切な静電容量が使用されていないと、周波数誤差がデータシートの仕様を超える可能性があります。発振器 IC には集積チップ容量がある場合とない場合があり、最良の周波数精度を確保するには、発振器 IC のプリント基板接続、ボンド ワイヤ、およびリード フレームからの寄生容量とともに考慮する必要があります。

対照的に、MEMS 発振器は、共振器と発振器/PLL IC を 1 つのパッケージに統合しているため、共振周波数を調整するための外部コンデンサが必要ありません。

クリスタルドライブレベル

発振回路が水晶振動子をオーバードライブしないように注意する必要があります。共振器をオーバードライブすると、水晶共振器の劣化が加速する可能性があり、極端なレベルでは水晶が損傷する可能性があります。対照的に、MEMS 共振器は経年劣化を起こしません。

2. MEMS発振器は品質と信頼性がはるかに優れています

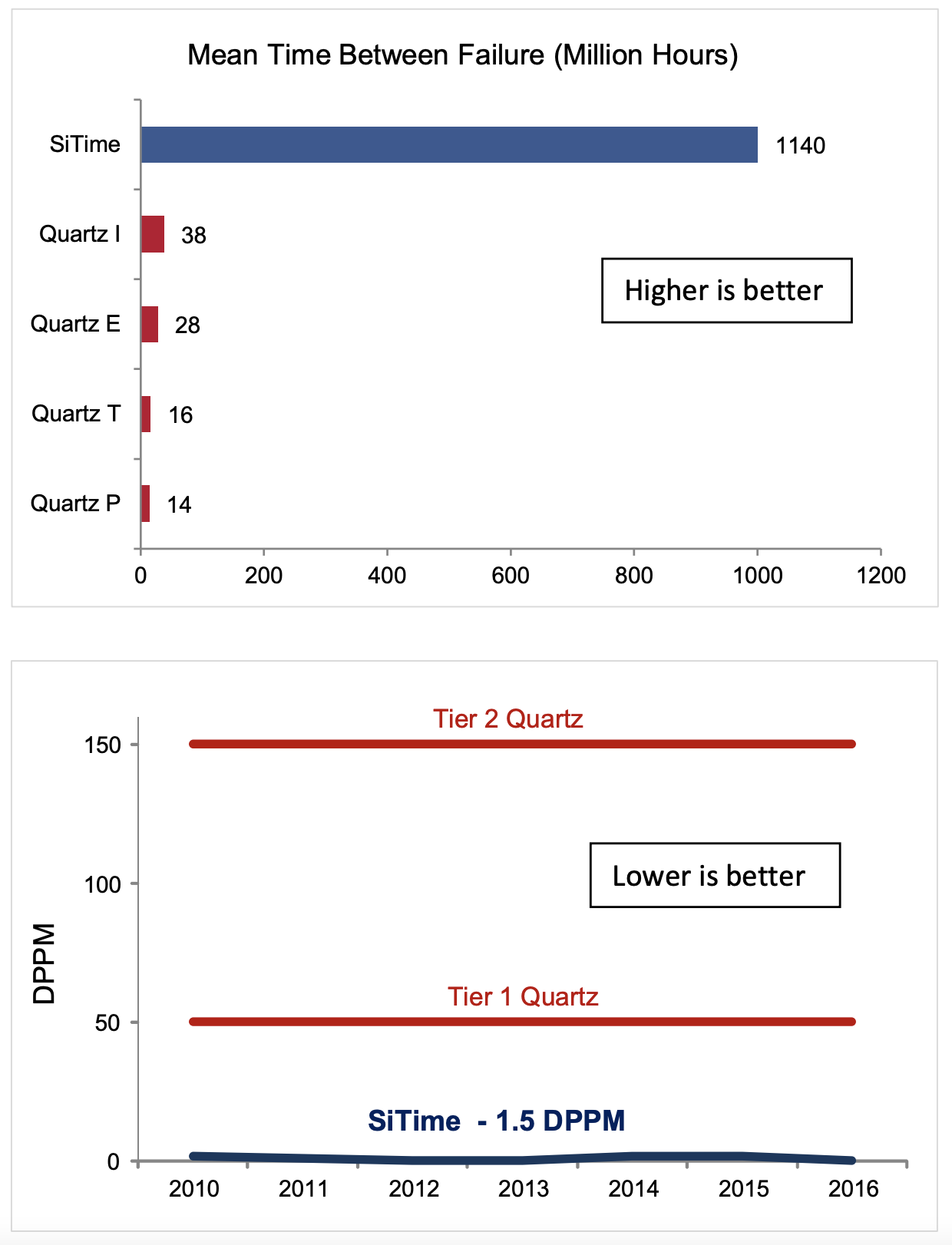

品質と信頼性は非常に重要です。会社の評判が危険にさらされるだけでなく、やり直しにはコストと時間がかかる可能性があります。さらに、屋外に展開され、環境ストレスにさらされるシステムは、特に堅牢である必要があります。水晶共振器は成熟した技術ではありますが、通常はイオン ビームで金属電極をアブレーションすることによって、個々の共振器を目的の周波数に調整するかなり複雑な製造プロセスが必要です。このステップは結晶がカプセル化される前に行われるため、共振器が汚染されやすくなります。このプロセスと他のクォーツ製造の複雑さにより、クォーツの平均故障間隔 (MTBF) は 1,400 万時間から 3,800 万時間という低さになります。欠陥部品/百万分率 (DPPM) は、最高のクォーツ メーカーでは最大 50、ティア 2 クォーツ サプライヤーでは 150 に達します。

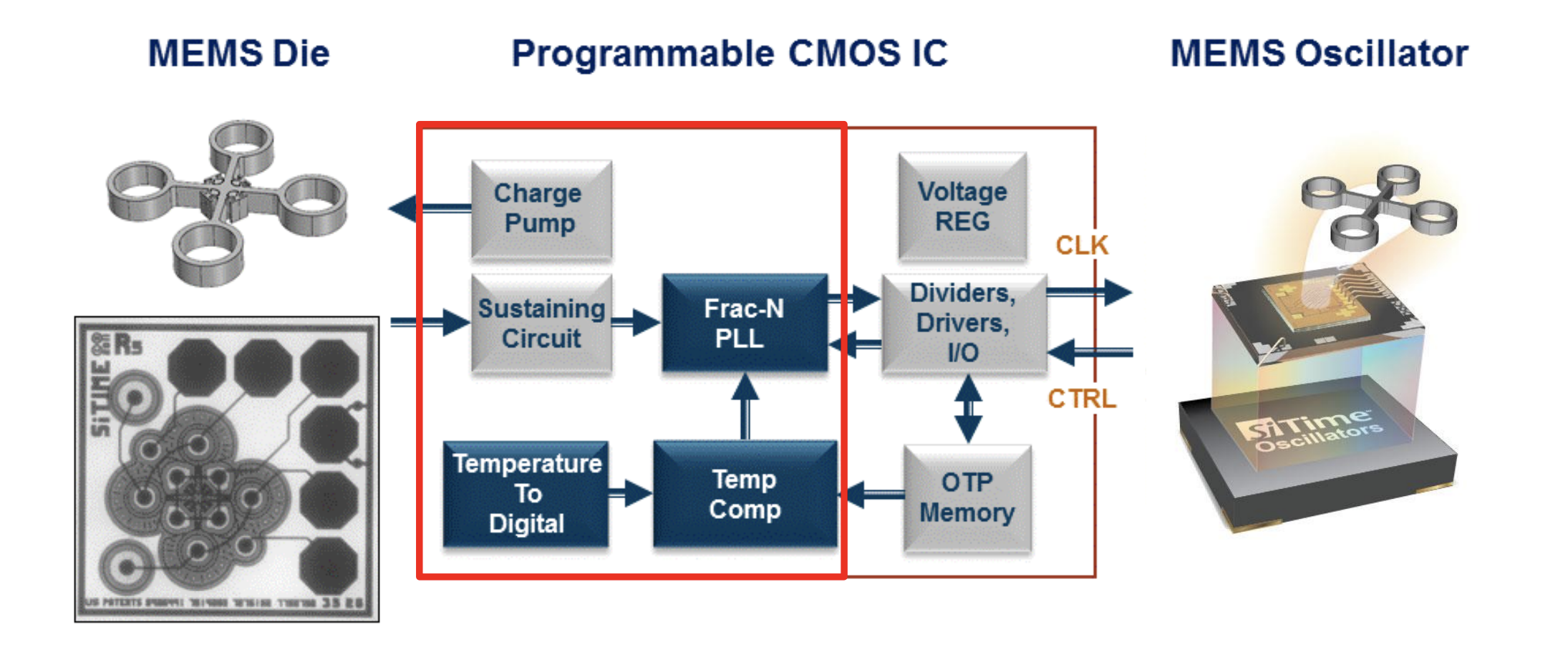

水晶の特殊な製造プロセスとは対照的に、MEMS 発振器メーカーは標準的な半導体バッチ モード技術を使用します。これには、共振器と発振器 IC のウェハ レベルの製造、およびプラスチック カプセル化による標準リード フレームへのダイ ボンディングが含まれます。 SiTime MEMS 共振器ダイは、純粋なシリコンの単一の機械構造から作られています。 SiTime MEMS の製造中、エピシール プロセスを使用して共振器を洗浄し、その後ポリシリコンを堆積して構造を封止します。超クリーンなハーメチック真空シールにより、共振器構造が保護され、汚染から解放され、経年劣化のメカニズムが排除されます。

その結果、SiTime 発振器の DPPM と MTBF は水晶よりも約 30 倍優れており、厳しい環境ストレスに耐え、エンドユーザーに高品質の製品を提供する非常に信頼性の高い技術プラットフォームを提供します。

3. MEMS 低周波発振器は基板占有面積を 65% 削減

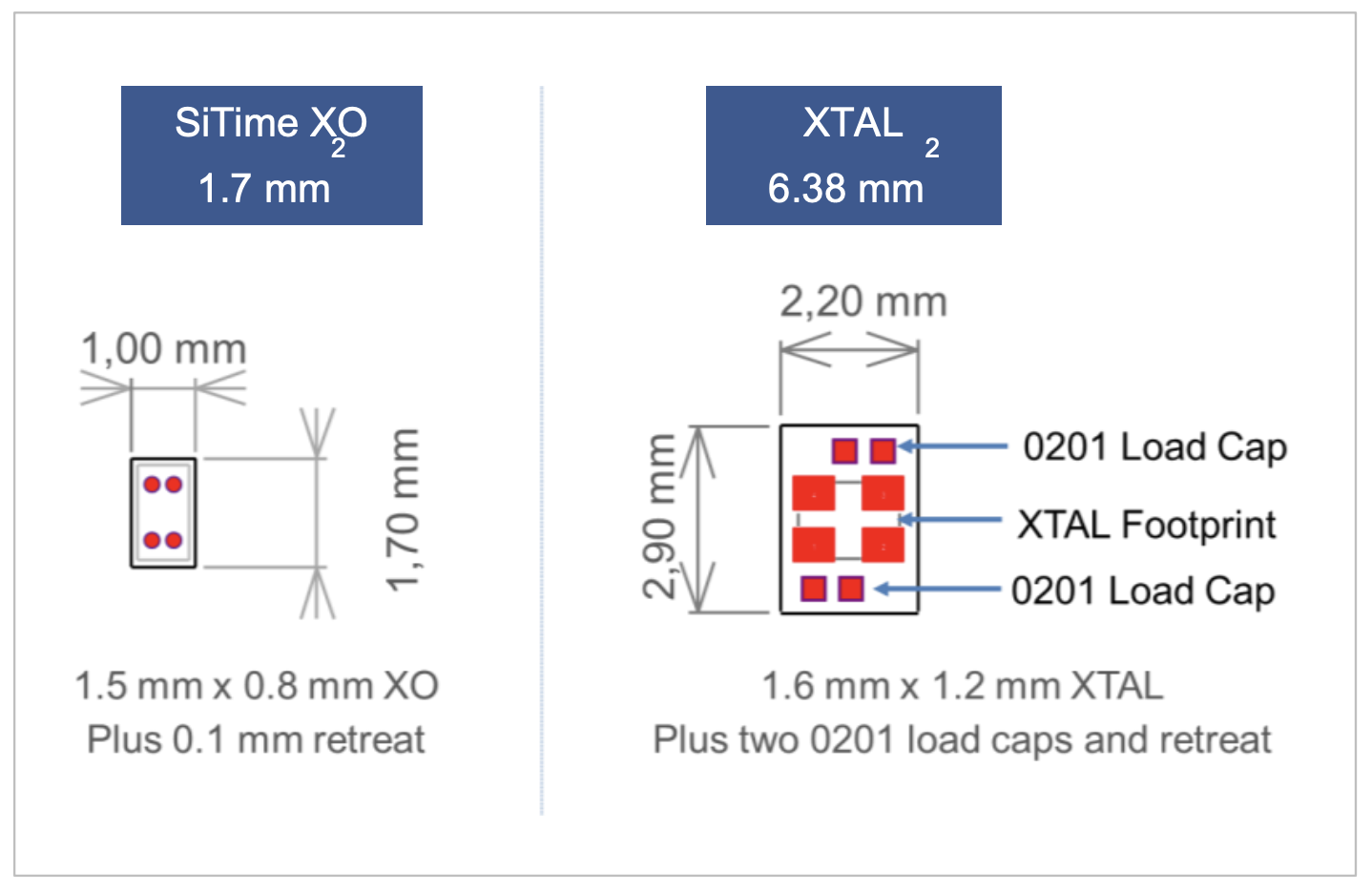

発振器は完全に統合されたソリューションであり、電源デカップリング キャップなどの外部コンポーネントは必要ありません。 SiTime の 1.5 mm x 0.8 mm (1508) の設置面積は、最小の水晶振動子の設置面積 1.6 mm x 1.2 mm よりも小さいです。また、32 kHz 水晶振動子に必要な負荷コンデンサを考慮すると、XTAL ソリューションの合計基板面積は 3 倍以上大きくなります。

4. 発振器は複数の負荷を駆動できるため、コスト、BOM、基板スペースが削減されます。

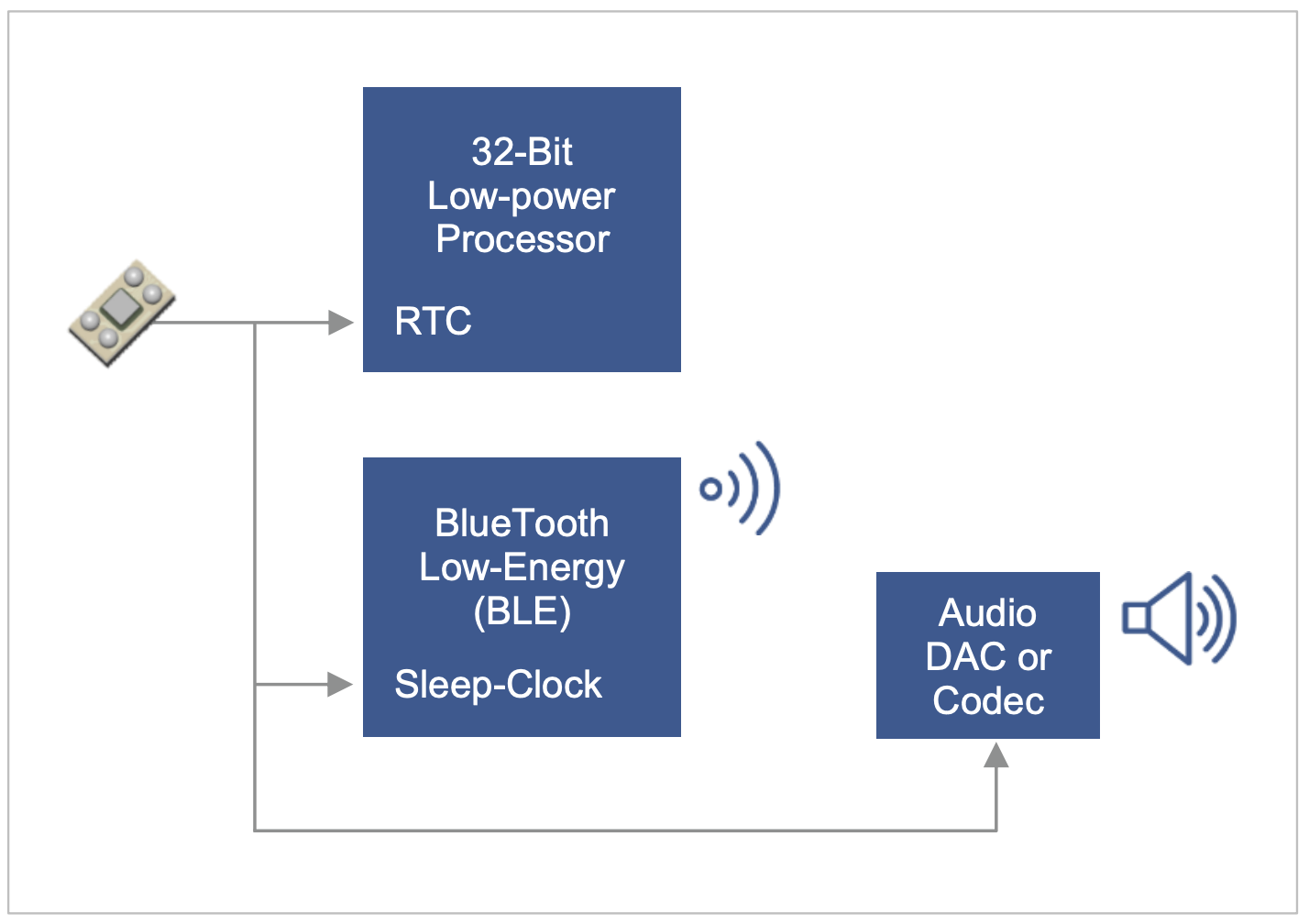

発振器は、通常、駆動強度に応じて 2 ~ 3 つの負荷を駆動できる出力ドライバーを備えたアクティブ回路です。これにより、発振器で複数の水晶振動子とそれに関連するコンデンサを置き換えることができ、BOM、システムコスト、基板面積がさらに削減されます。

5. MEMS 発振器は EMI の影響を非常に受けにくい

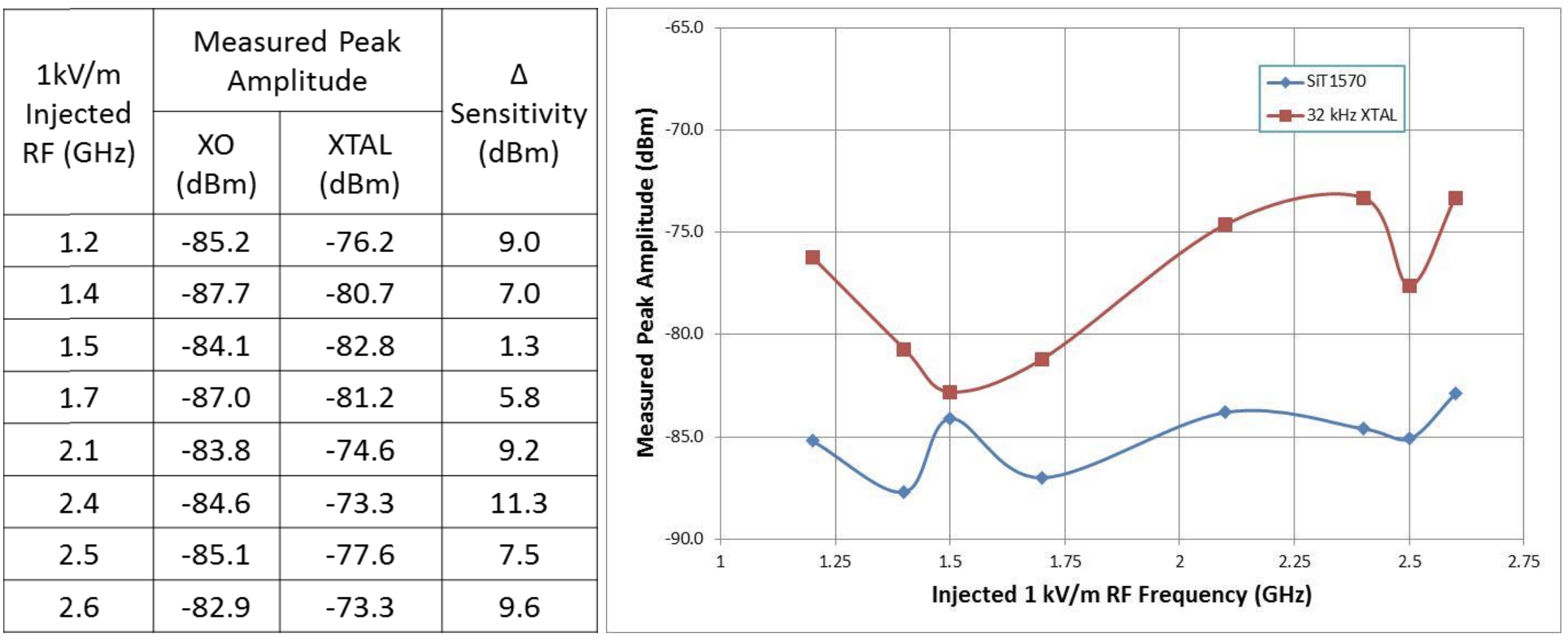

ほとんどのシステムで一般的な電磁エネルギーは、水晶振動子を発振回路を含む IC に接続する露出した PCB 配線によって拾われる可能性があります。このノイズは発振回路に結合され、出力に渡される可能性があり、システムにジッターやノイズを加える可能性があります。ただし、統合発振器では、共振器と発振器 IC の間に露出した PCB 接続がなく、MEMS 共振器を IC に接続するボンドワイヤまたはボールは非常に短いです。これにより、MEMS 発振器は EMI に対する感度が大幅に低くなります。次の表とプロットに示すように、SiTime 発振器は水晶発振器よりも最大 11.3 dBm (線形スケールで 134 倍) 感度が低くなります。

このテストは、試験対象デバイス (DUT) が取り付けられている横電磁 (TEM) セルに電磁エネルギーを注入する IEC 62132-2 規格に従って実行されました。

6. MEMS 発振器は振動の影響を非常に受けにくい

無線基地局やスモールセルなど、非常に安定した周波数を必要とする一部のシステムでは、振動によりシステム障害やサービスの中断が発生する可能性があります。

MEMS 振動子の質量は水晶振動子の質量に比べて約 1,000 ~ 3,000 分の 1 であるため、MEMS 発振器は耐振動性を備えています。これは、衝撃や振動などによって MEMS 構造に与えられる特定の加速度が、同等の水晶よりもはるかに小さな力となり、したがってはるかに低い周波数シフトを引き起こすことを意味します。 5 ページの図は、SiTime MEMS 発振器は水晶発振器と比較して振動感度が 10 分の 1 以上低い (優れている) ことを示しています。この数値は受動水晶共振子ではなく水晶発振器の測定に基づいていますが、水晶共振子でも同等の結果が期待されることに注意してください。

7. MEMS 発振器はあらゆる周波数ですぐに利用可能

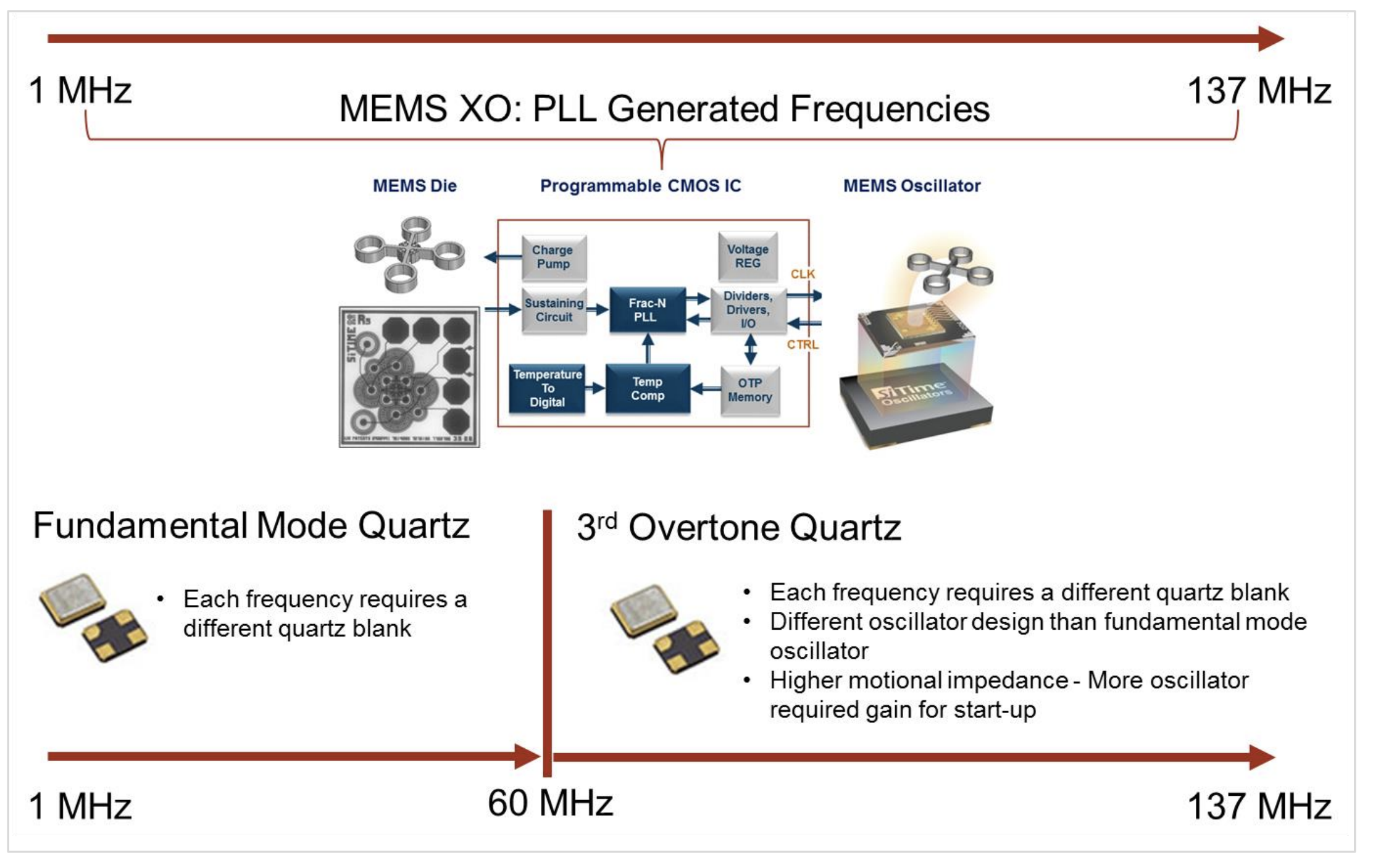

クォーツの供給インフラにはいくつかの制約があり、そのためリードタイムが 12 ~ 16 週間程度、あるいはそれ以上かかる場合があります。制約の 1 つは、セラミック パッケージのサプライヤーの数が限られていることです。もう 1 つの制約は、利用できる周波数オプションが限られていることです。水晶製品では、プログラマブル位相ロック ループ (PLL) が使用されない限り、すべての周波数に異なる水晶カットが必要です。したがって、標準外の周波数の場合はリードタイムが非常に長くなる可能性があります。

水晶共振器とは対照的に、MEMS 共振器は標準的な共振器構成に基づいています。 MEMS 発振器の出力周波数は、PLL をさまざまな乗算値にプログラムすることによって生成されます。これにより、6 桁の精度で非常に広い周波数範囲が可能になります。さらに、シリコン MEMS 発振器は、標準的な半導体プロセスとパッケージングを使用して製造されます。 MEMS 発振器ベンダーは非常に大規模な半導体業界のインフラストラクチャを活用しているため、容量は事実上無制限です。

MEMS 発振器のサンプルは、標準外の周波数であっても 1 日以内にプログラムして入手できます。 SiTime の低コストのTime Machine II プログラマとフィールド プログラマブル発振器を使用することで、設計者は研究室で発振器を即座にプログラムして、デバイスの動作範囲内で任意の周波数、任意の電源電圧、任意の安定性を備えたデバイスを作成できます。生産リードタイムはわずか 6 ~ 8 週間です。

8. 製品ファミリー全体に対して 1 つの認定資格

コンポーネントを最終用途 (システム) 条件に適合させるには、かなりの時間とリソースが消費される可能性があります。ただし、MEMS 発振器を使用すると、認定の労力を軽減できます。 SiTime 製品は、基本製品ファミリー内の各デバイスが広範囲の周波数、供給電圧、安定性を生成できるようにするプログラム可能なプラットフォームに基づいています。たとえば、特定の出力周波数で SiTime デバイスを認定するためにリソースが投資されており、新しいボード設計で別の周波数が必要な場合、既存の認定データを新しい周波数の部品に拡張できます。

対照的に、各 XTAL 周波数には異なる水晶ブランクが必要です。また、設計で 60 MHz を超える周波数が必要な場合は、基本モード水晶以外の別の技術が使用されることがよくあります。第三倍音水晶は、より高い周波数によく使用されます。このモードでは、信頼性の高い起動を保証するために追加の課題 (つまり、基本モードよりも高い動作インピーダンスと異なる発振回路) が発生する可能性があり、これには認定が必要です。

まとめ

固有の制限にもかかわらず、水晶は数十年にわたって電子タイミングの標準となってきました。 SiTime の MEMS 発振器はこれらの制限を克服し、従来の水晶振動子と比較して多くの利点を提供します。設計者は、XTAL に伴う頭痛の種や制限を受け入れる必要がなくなりました。

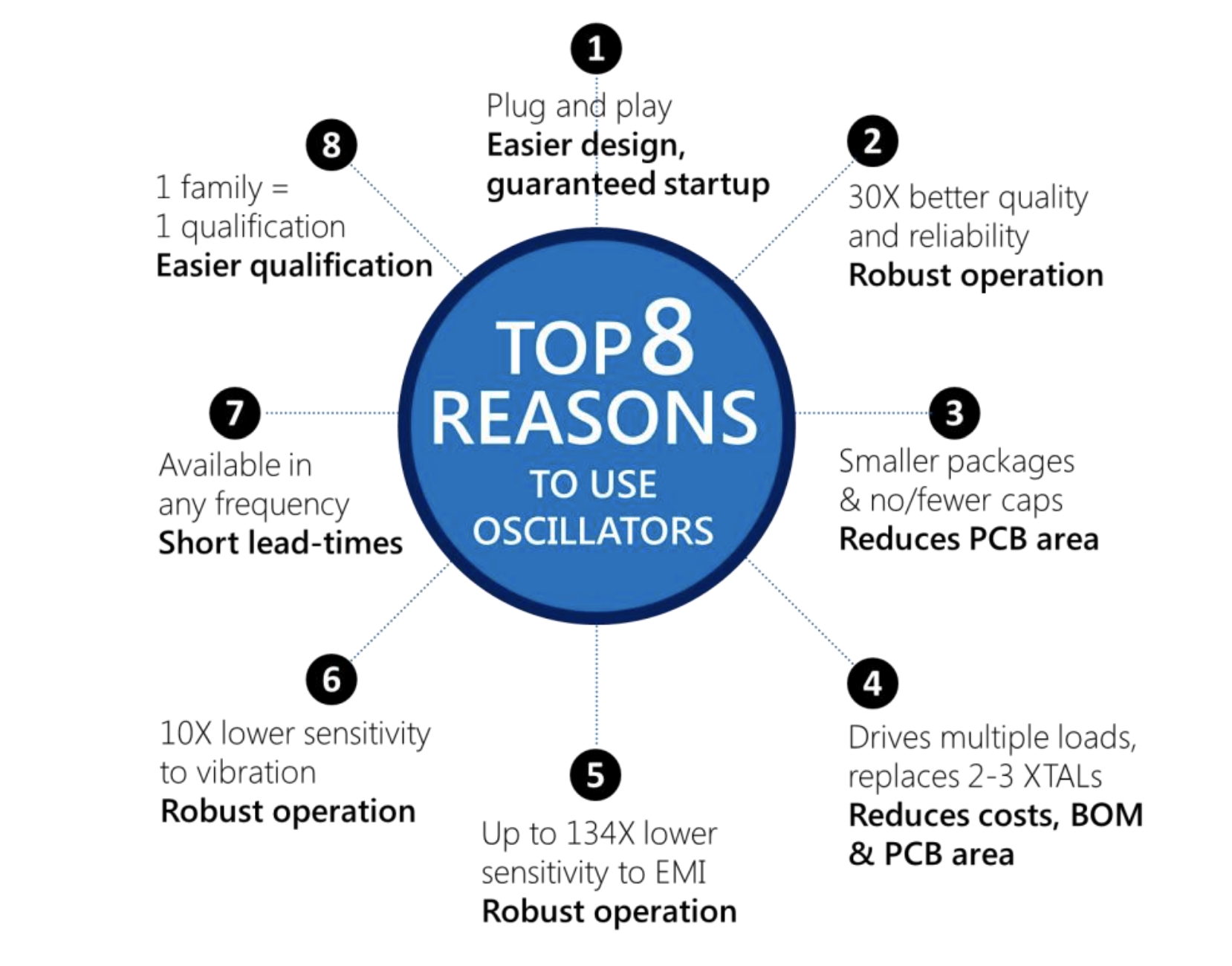

XTAL を MEMS 発振器に置き換える主な 8 つの理由は次のとおりです。

- 発振器は「プラグアンドプレイ」です - 設計がはるかに簡単で、起動が保証されています

- 30 倍優れた品質と信頼性 – コストを削減し、堅牢性を向上

- パッケージが小さく、キャップがないか少ない - PCB 面積が削減される

- 2 ~ 3 個の水晶振動子を置き換えて複数の負荷を駆動 – コスト、BOM、および PCB 面積を削減

- 電磁エネルギーに対する感度が最大 134 分の 1 に低下 – より堅牢

- 振動に対する感度が 10 分の 1 に低下 – より堅牢

- あらゆる頻度で利用可能 - リードタイムが非常に短い

- 1 つの MEMS 製品で広い周波数範囲をカバーし、認定作業を軽減します