SiT92206 は、最大 2.1 GHz の周波数をサポートする 6 出力の低ジッタ ファンアウト クロック バッファです。低ジッタ、高周波クロック/データ分配およびレベル変換アプリケーションに最適です。

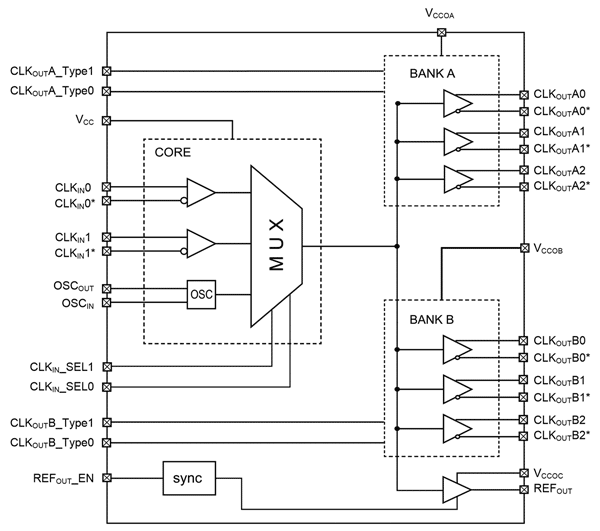

バッファは、シングルエンドまたは完全差動のプライマリまたはセカンダリ クロック ソースからのクロック入力を使用できます。選択されたクロックは、2 つの出力ドライブ バンク A、B、および 1 つの LVCMOS 出力に分配できます。

各バンクの出力ドライバは、LVPECL、LVDS、HCSL、または HIZ モードに個別にプログラムできます。LVCMOS クロック出力は、選択したクロックに同期され、グリッチのない方法で有効化または無効化できます。

SiT92206 は、3.3 V/2.5 V コア電源と 3 つの独立した 3.3 V/2.5 V 出力電源で動作します。LVCMOS 出力ドライバは 1.8 V で動作できます。

| "スペック" | "値" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 6x6 mm, 36-pin QFN |

| Buffer Type | Fanout |

| Number of Inputs | 3 |

| Number of Outputs | 6 Differential |

| Input Type | LVPECL, LVDS, LVCMOS, SSTL, HCSL |

| Input Frequency Range | 0 Hz to 2.1 GHz |

| Output Type | LVPECL, LVDS, HCSL, LVCMOS |

| Output Frequency Range | 0 Hz to 2.1 GHz |

| Additive Phase Jitter (rms) | 55 fs (typ.) |

| Propagation Delay, Typical | 1.4 ns |

| Output-Output Skew, Typical | 30 ps |

| Availability | Sampling |

-

6x6 mm, 36-pin QFN Clock Buffer package

- 3:1入力クロック選択。

- 2 つのユニバーサル クロック入力は最大 2.1 GHz で動作し、LVPECL、LVDS、LVCMOS、CML (AC 結合のみ)、HCSL、SSTL、またはシングル エンド クロックを受け入れます。

- LVPECL、LVDS、HCSL、または HIZ モードに個別にプログラムできる 2 つの出力ドライバ バンク A と B。

- コア電源電圧 3.3 V/2.5 V と差動出力ドライバ用出力電源 3.3 V/2.5 V によるレベル変換。

- 単一の LVCMOS 出力ドライバの 3.3 V/2.5 V/1.8 V 動作。

- LVPECL/LVDS モードでは高い PSRR -70/-73 dBc。

- PCI-e Gen 1 から Gen 5 をサポートします。

Apply Filters

| Resource Name | Resource Type | Date | Format | Size |

|---|