このアプリケーション ノート [AN10029] の PDF をダウンロードしたい場合は、 ここをクリックしてください。

1. はじめに

差動発振器は高性能アプリケーションで使用され、電源ノイズに対する高い堅牢性などのいくつかの利点を提供します。このアプリケーション ノートでは、LVPECL、LVDS、または HCSL 出力ドライバを使用した、表 1 にリストされている SiTime 差動発振器ファミリの終端に関する推奨事項を示します。 CML または HCSL クロック入力を LVPECL 出力で駆動するためのインターフェイスについても説明します。

SiTime 発振器の一般的な出力の立ち上がり時間と立ち下がり時間は 250 ps ~ 600 ps の範囲にあり、これにより PCB 上の短い配線であっても、インピーダンス整合が必要な分布伝送線路のように動作します。したがって、差動信号用のトレースは、長さが一致した制御されたインピーダンス伝送線路として設計することをお勧めします。最高の信号整合性と最低の EMI を実現するには、これらのトレースを適切に終端する必要があります。インピーダンス整合に加えて、終端ネットワークは受信機側の DC バイアスと AC 電圧振幅にも影響を与えます。

表 1: SiTime 差動発振器

デバイスファミリー | 発振器の種類 | 出力ドライバーの種類 |

差動発振器 | LVPECL、LVDS | |

差動発振器 | LVPECL、LVDS | |

差動発振器 | LVPECL、LVDS | |

SiT9365 | 高性能差動発振器 | LVPECL、LVDS、HCSL |

高性能差動発振器 | LVPECL、LVDS、HCSL | |

高性能差動発振器 | LVPECL、LVDS、HCSL | |

車載向け高性能差動発振器 | LVPECL、LVDS、HCSL | |

車載向け高性能差動発振器 | LVPECL、LVDS、HCSL | |

DE を備えた電圧制御発振器 (VCXO) | LVPECL、LVDS | |

SiT3822 | DE 付き電圧制御発振器 (VCXO) | LVPECL、LVDS |

DE を備えた高性能電圧制御発振器 (VCXO) | LVPECL、LVDS、HCSL | |

DE を備えた高性能電圧制御発振器 (VCXO) | LVPECL、LVDS、HCSL | |

DE を備えた電圧制御発振器 (VCXO) | LVPECL、LVDS | |

DE を備えた電圧制御発振器 (VCXO) | LVPECL、LVDS | |

DE を備えた高性能スペクトラム拡散発振器 (SSXO) | LVPECL、LVDS、HCSL、CML | |

DE を備えた高性能デジタル制御発振器 (DCXO) | LVPECL、LVDS、HCSL | |

DE を備えた高性能デジタル制御発振器 (DCXO) | LVPECL、LVDS、HCSL | |

DE を備えた温度制御発振器 (TCXO) | LVPECL、LVDS | |

DE を備えた温度制御発振器 (TCXO) | LVPECL、LVDS |

2. LVPECL出力

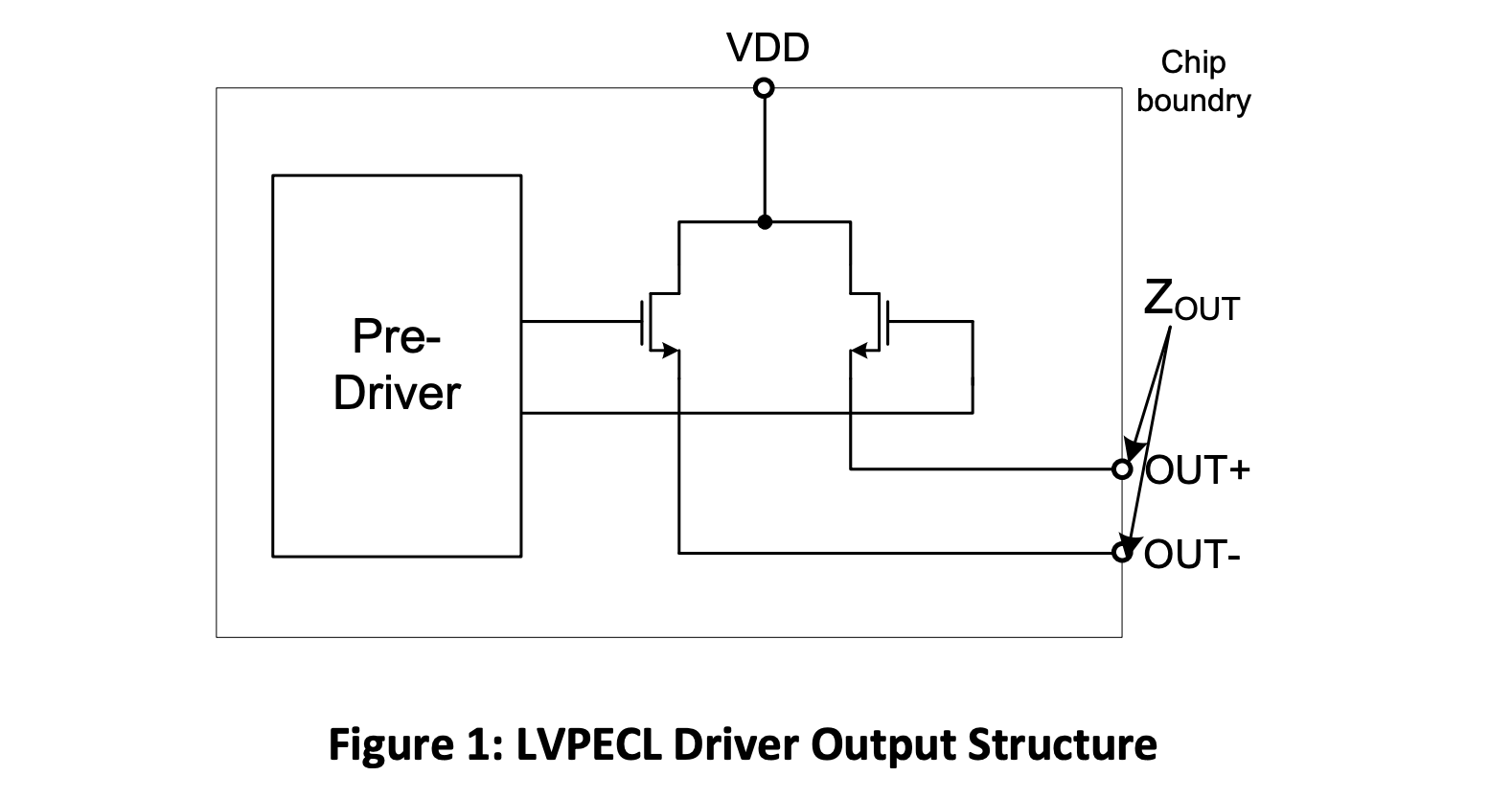

図 1 は、SiTime 差動発振器ファミリで使用される低インピーダンス LVPECL ドライバ構造を示しています。ドライバーの出力段は、共通ソース構成の一対の NMOS トランジスタで構成されます。一般的なドライバーのインピーダンスは約 5Ω ~ 10Ω です。

2.1 DC 結合アプリケーションの終端に関する推奨事項

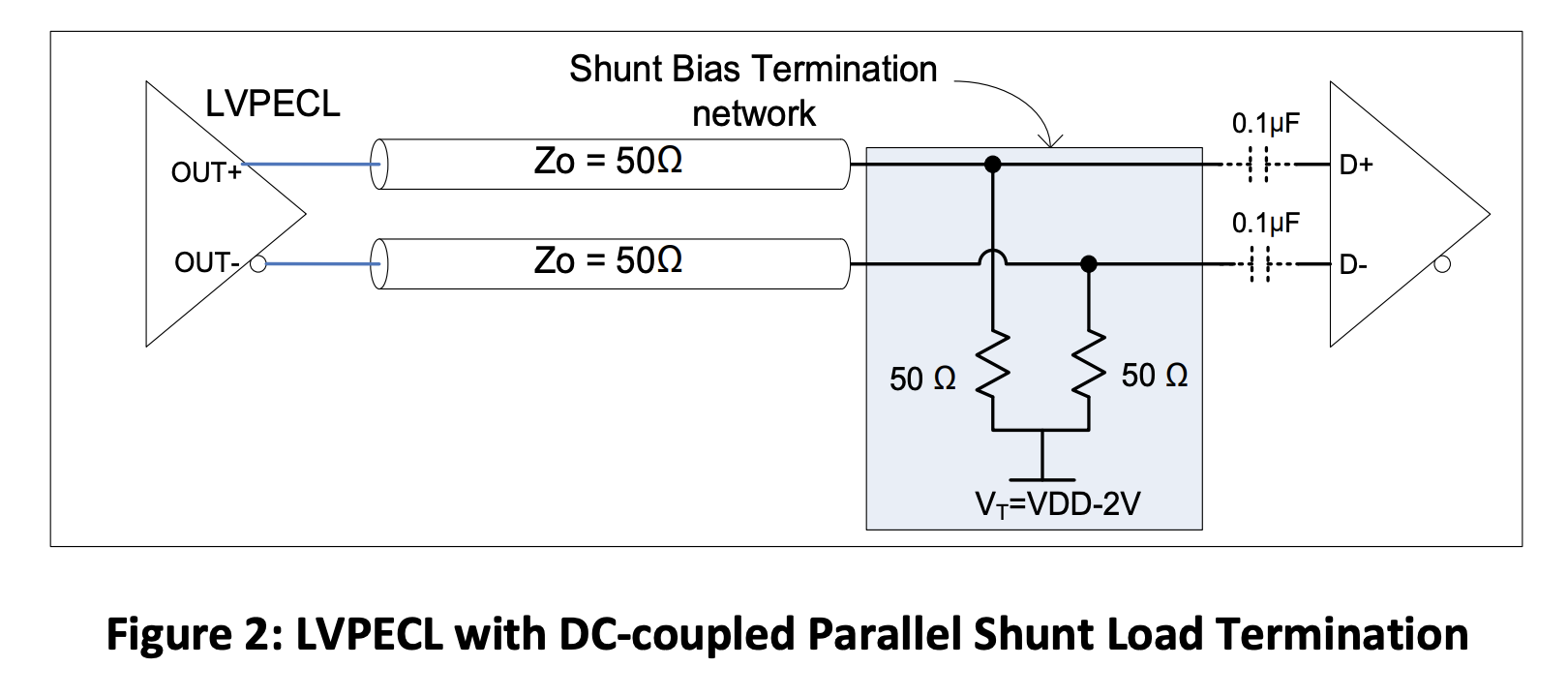

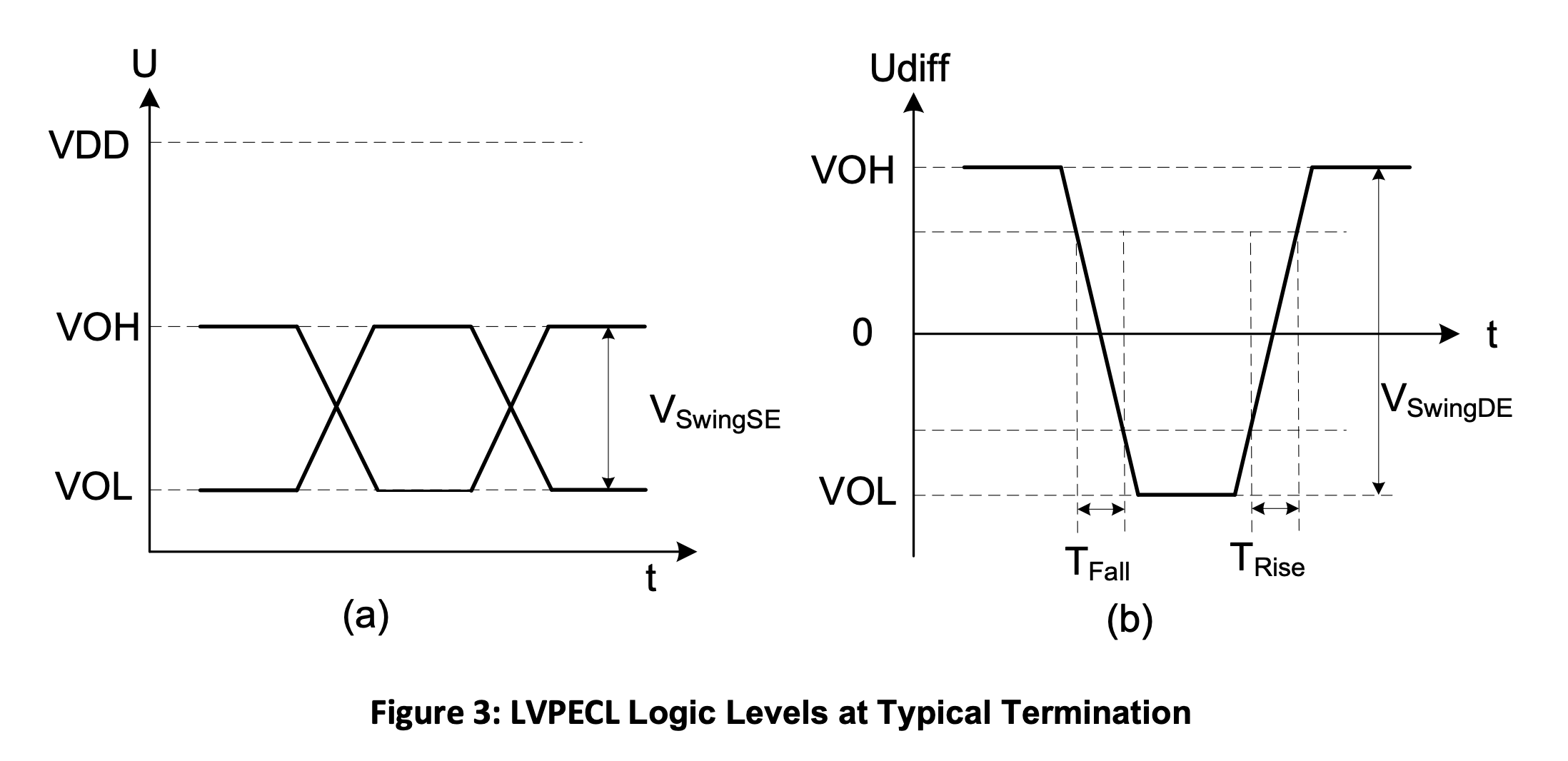

LVPECL は通常、図 2 に示すように負荷側で終端されます。出力は 50Ω 抵抗を使用して終端電圧 (VT) に接続され、伝送線路との良好なインピーダンス整合を実現します (負荷終端解析については付録 A を参照)。図 3(a) は、一般的な終端を備えた LVPECL 出力のシングルエンド波形を示しています。標準的な電圧出力ハイ (VOH) と電圧出力ロー (VOL) の信号レベルは、それぞれ VDD – 0.9V と VDD – 1.7V です。データシートに指定されている VOH および VOL の制限値は、部品ごとの出力ドライバのインピーダンス変動および外部負荷条件を考慮しています。

正出力と負出力の間の差動波形の電圧振幅 (VDiff = VOUT+ -VOUT-) は、シングルエンド信号電圧振幅の 2 倍です。標準的な LVPECL 差動スイングは 1.6V です。図 3(b) は、差動波形に対して 20% ~ 80% の立ち上がり時間と立ち下がり時間がどのように定義されるかを示しています。

VOH、VOL、および電圧スイングは終端に依存し、デフォルト以外の終端が使用されている場合は異なる可能性があることに注意してください。

LVPECL レシーバに終端が内蔵されていない場合は、外部 50Ω 終端抵抗をレシーバのできるだけ近くに配置して、信号の整合性の問題を引き起こす可能性がある未終端のスタブを減らす必要があります。伝送線路は負荷側でのみ終端する必要があります。

別の終端電圧が容易に利用できないアプリケーションでは、テブナン等価ネットワークを形成するプルアップ抵抗とプルダウン抵抗を使用して 50Ω 伝送線を終端できます (図 4 を参照)。このようなネットワークは、レシーバー入力で VDD – 2V の DC バイアス電圧と実効 50Ω 終端インピーダンスを確立します。抵抗値は 3.3V と 2.5V の電源電圧では異なることに注意してください。

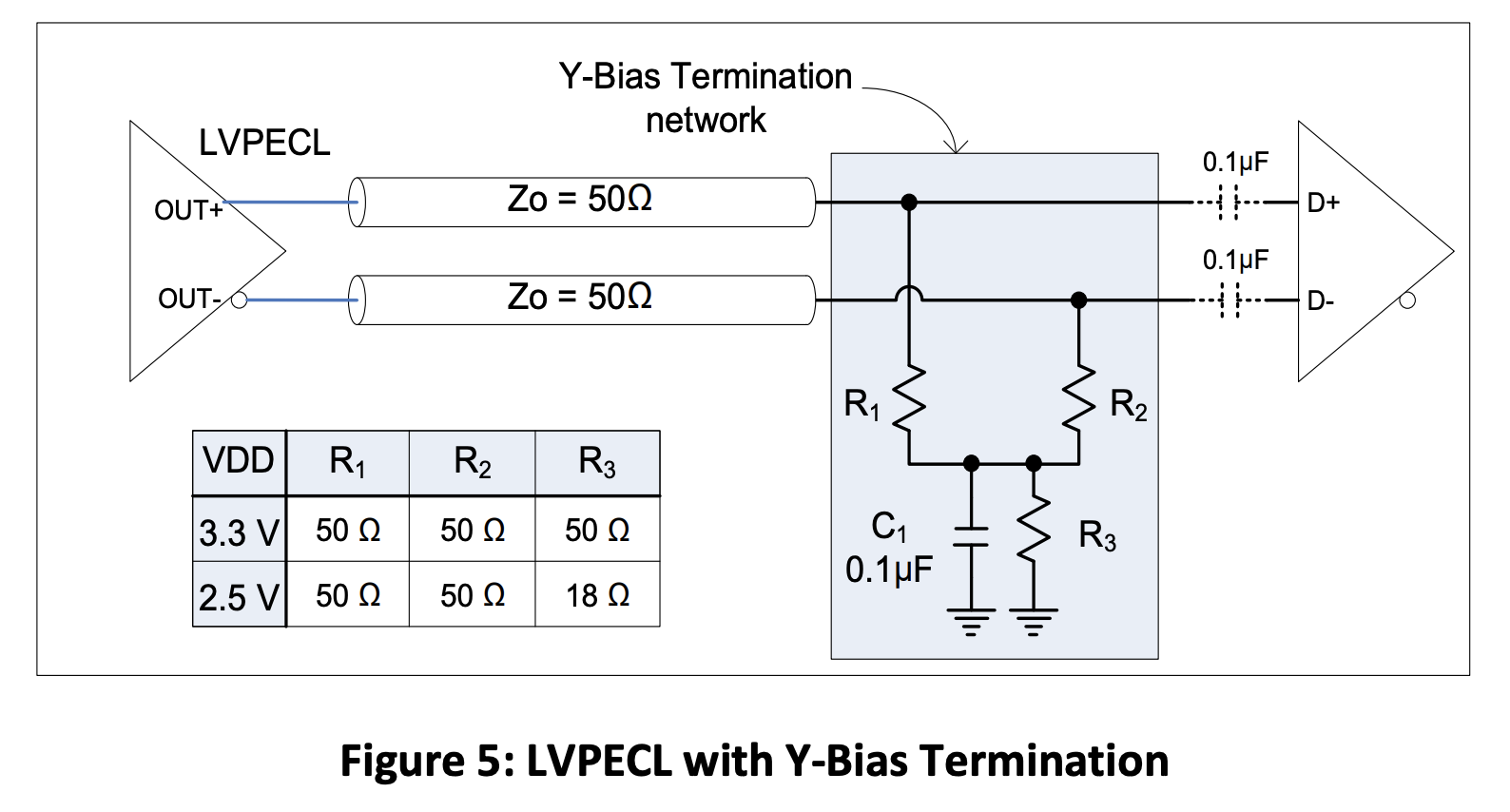

ほとんどの場合、テブナン等価終端は適切に機能しますが、差動ペアの両側のトレース間または抵抗ネットワーク間に重大な不一致がある場合、またはレシーバがコモンモード ノイズに敏感すぎる場合は、電源ノイズの影響を受けやすくなる可能性があります。 。図 5 は、VDD への接続や追加の終端電圧源へのアクセスを必要とせずに、VDD – 2V の実効終端電圧を提供する Y バイアス終端ネットワークを示しています。終端電圧は、抵抗 R3 を通過する差動ペア電流の合計によって生成されます。コンデンサ C1 は、終端電圧で AC グランドを生成するために使用されます。

2.2 AC結合アプリケーションの終端に関する推奨事項

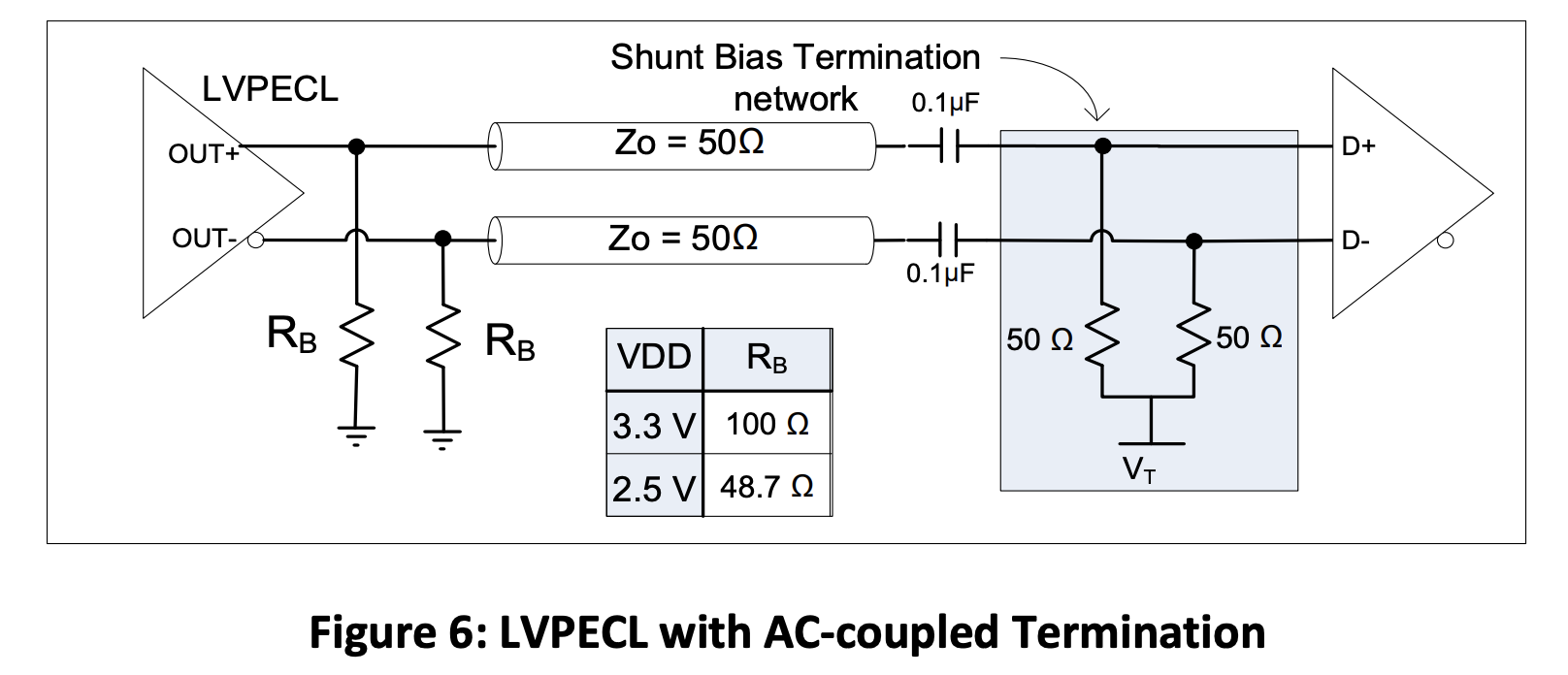

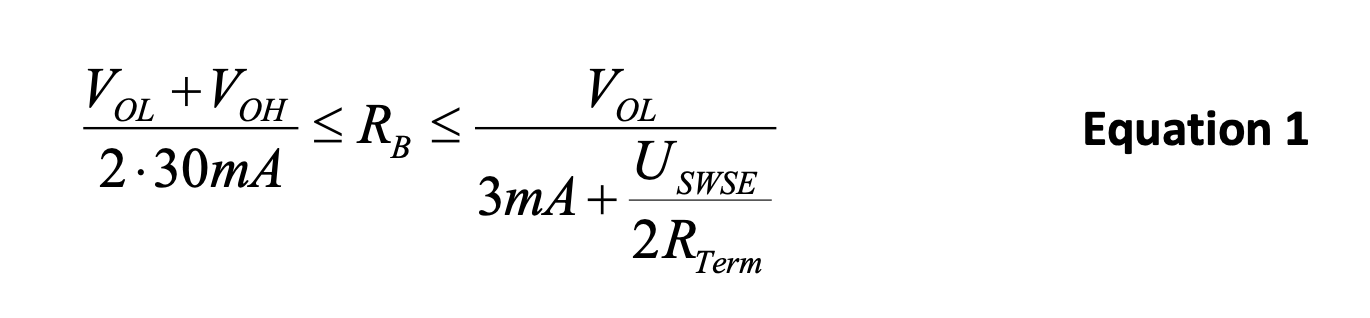

LVPECL レシーバは、DC 結合または AC 結合のいずれかで接続できます。レシーバ側と発振器側の DC バイアス電圧が異なる場合は、AC カップリング コンデンサが必要です。場合によっては、図 6 に示すように、終端ネットワークを AC 結合する必要があります。LVPECL ドライバが適切に動作するには、出力トランジスタが完全にオフになってはいけないため、AC 結合コンデンサの前に追加のバイアス抵抗 RB を配置する必要があります。ドライバーに DC 電流経路を提供します。 RB の値は、ピンが Low 状態のときにドライバ ピンを流れる最小電流が 3 mA 以上、ドライバを流れる最大 DC 電流が 30 mA を超えないように選択されます。式 1 を使用して RB を推定できます。

式 1 では、USWSE はシングルエンド電圧振幅、RTerm は終端ネットワーク抵抗です。 SiTime は、3.3V 電源と 2.5V 電源にそれぞれ 100Ω と 48.7Ω の RB 値を使用することを推奨します。

LVPECL 並列負荷終端で最高の信号整合性を実現するには、次の推奨事項に従う必要があります。

- 終端ネットワークを受信機から 0.1 ~ 0.2 インチ以内に配置します。終端ネットワークを受信機に接続する長いトレースはスタブとして現れ、受信機入力での信号の完全性を低下させる可能性があります。

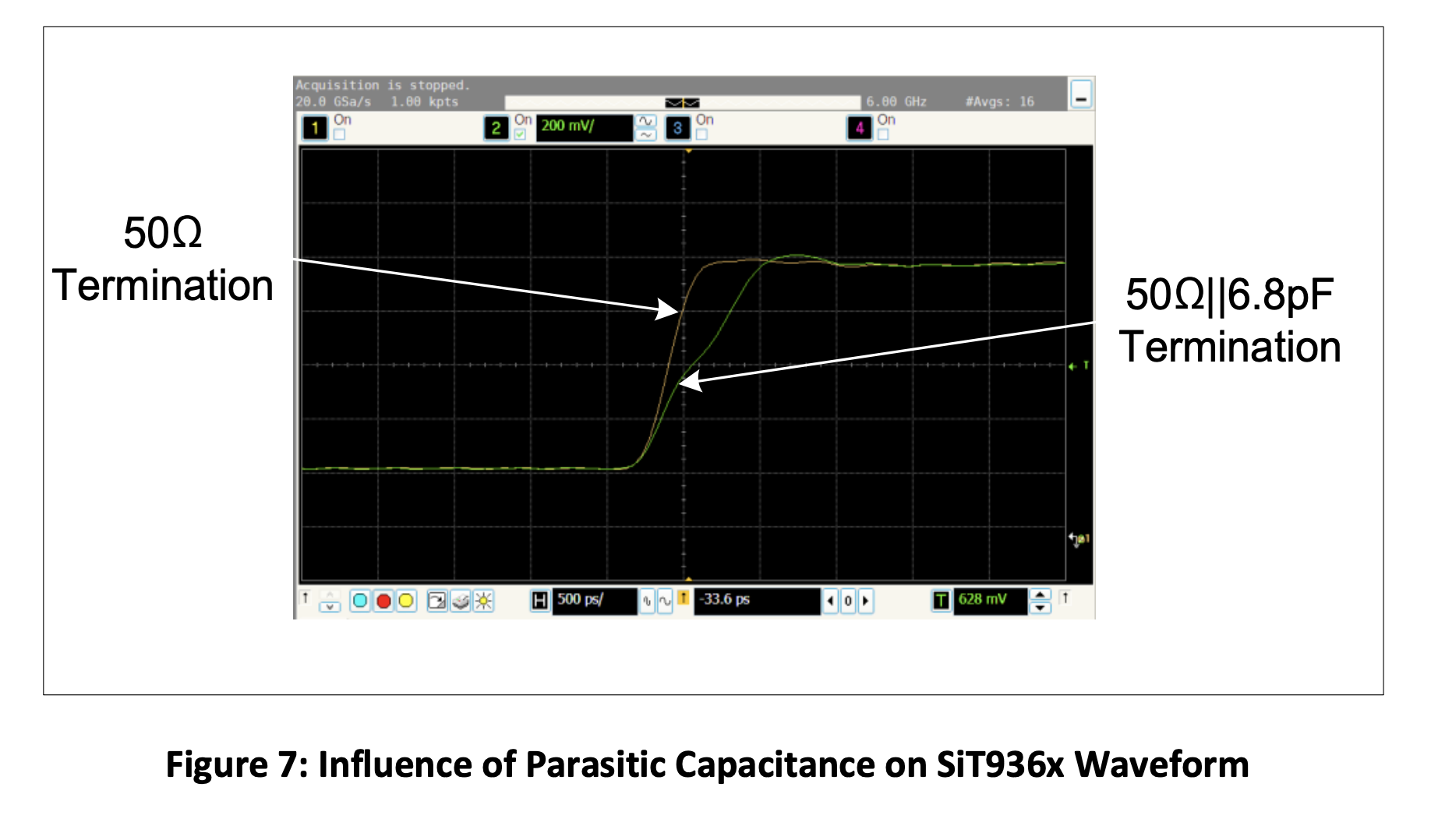

- レシーバー入力の容量性負荷を最小限に抑えます。高い容量性負荷は、高速信号エッジが受信機に到達するときに終端インピーダンスを低下させ、大きな負荷反射係数を引き起こします。この反射は、発生源で反射された後、わずかに減衰して負荷に戻ります。

3. LVDS出力

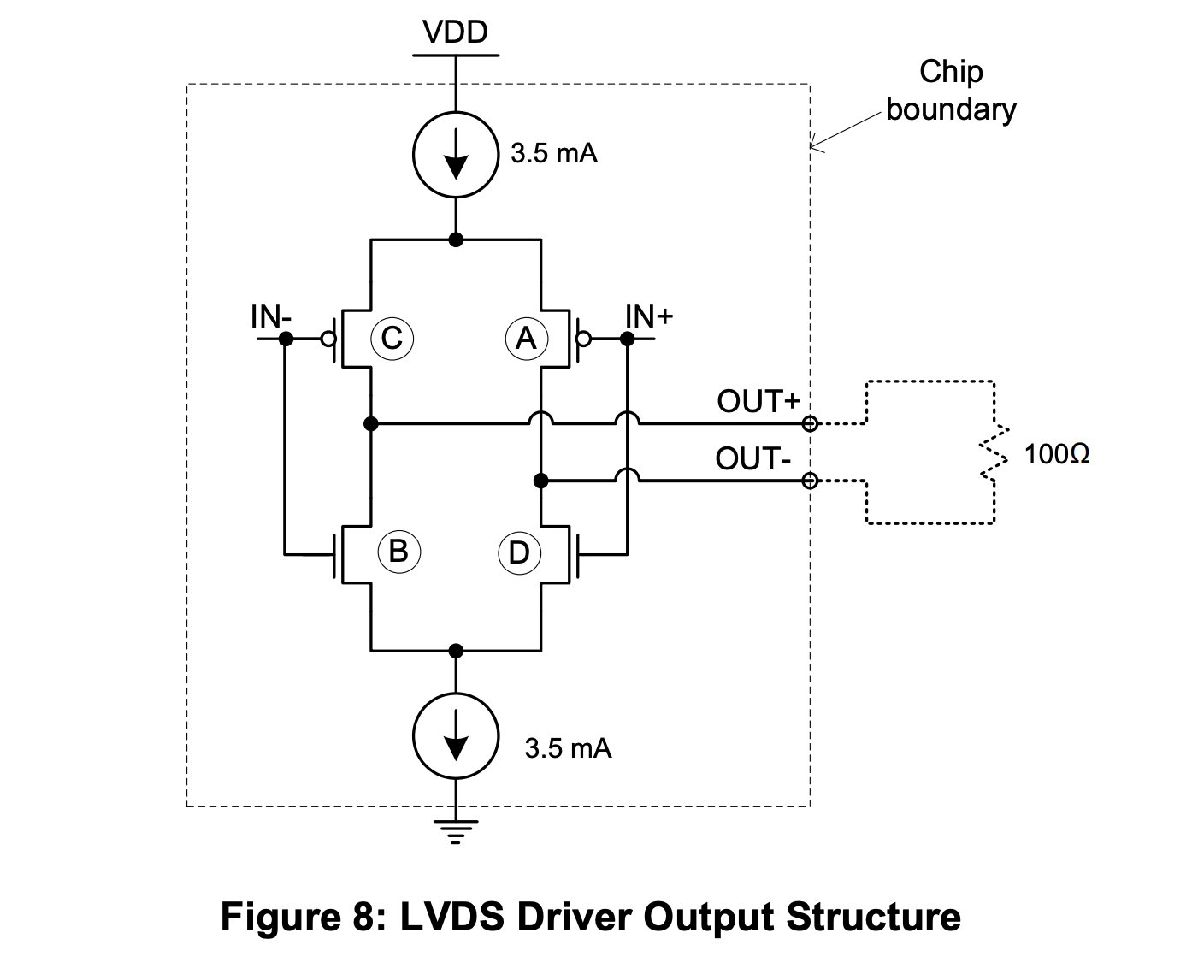

LVDS は、低消費電力と高いノイズ耐性を必要とする多くのアプリケーションに適した高速デジタル インターフェイスです。 LVDS 出力は、低電圧スイングの差動信号を使用して、高速でデータを送信します。図 8 は、「H」スイッチとも呼ばれるスイッチング ネットワークを介して差動出力に接続された 3.5 mA 公称電流源で構成される LVDS ドライバの出力構造を示しています。出力は通常、レシーバ入力間の 100Ω 抵抗で終端された 100Ω 差動伝送線に接続されます。抵抗値は伝送線路のインピーダンスと一致し、信号に電流経路を提供します。

ドライバには、VDD に関係なくコモンモードを公称 1.2 V に設定する回路が含まれています。したがって、ドライバを外部から特定の電圧にバイアスする必要はありません。また、発振器の実際の電源電圧を気にすることなく、LVDS 出力を任意の LVDS 入力に接続できます。

信号の切り替えは、A、B、C、D のラベルが付いた 4 つのトランジスタで行われます。レシーバのインピーダンスは一般に高いため、ドライバからの事実上すべての電流は 100Ω 抵抗を流れ、レシーバ間に 350 mV の電圧差が生じます。入力。図 8 では、信号 IN が Low の場合、トランジスタ A と B がオンになります。電流はトランジスタ A と 100Ω 抵抗を通って流れ、トランジスタ B を通って戻ります。信号 IN が High のとき、トランジスタ C と D はオンになります。電流はトランジスタ C と 100Ω 抵抗を通って流れ、トランジスタ D を通って戻り、レシーバの両端に -350mV の電圧が生じます。

受信機の観点から見ると、終端抵抗を流れる電流の方向によって、正または負の差動電圧が記録されるかどうかが決まります。正の差動電圧は論理ハイ レベルを表し、負の差動電圧は論理ロー レベルを表します。

3.1 DC 結合アプリケーションの終端に関する推奨事項

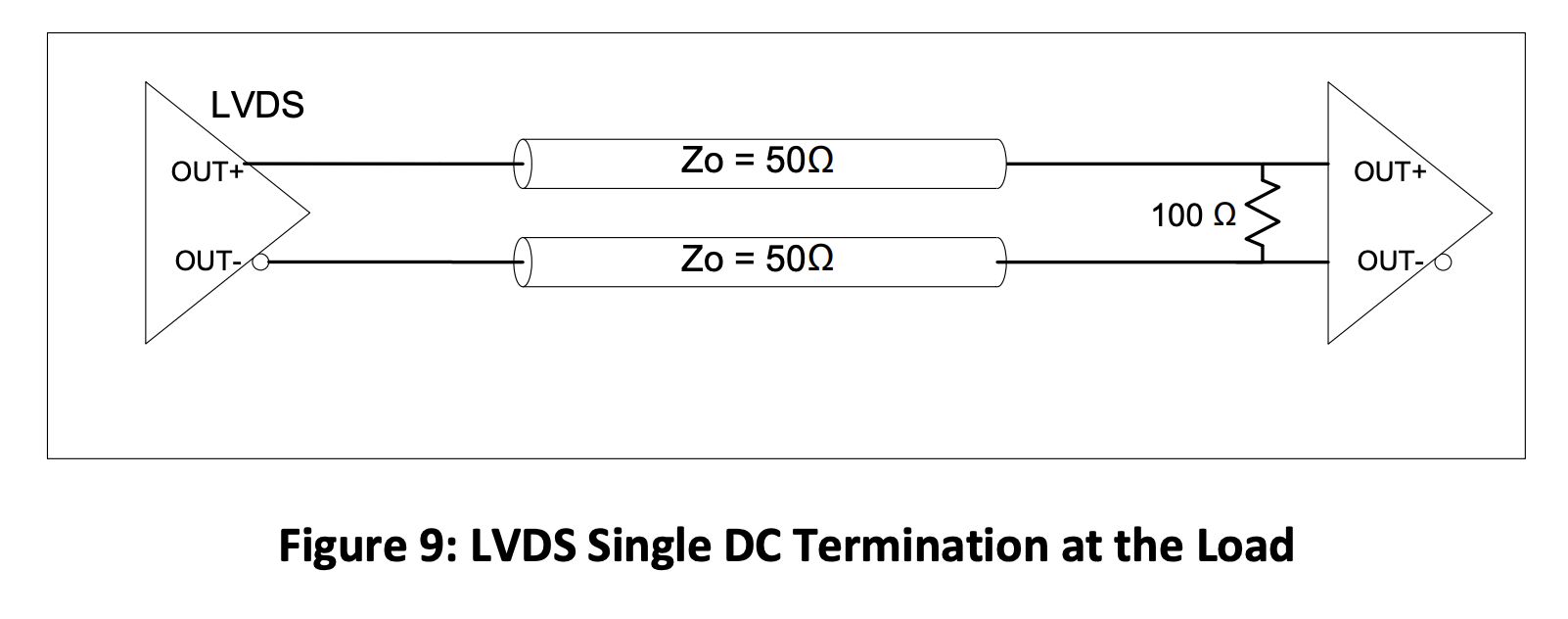

100Ω の差動トレースを備えた LVDS インターフェイスは、通常、レシーバーの差動入力間の 100Ω 抵抗によってレシーバー側で終端されます (図 9 を参照)。一部の受信機には 100Ω のオンチップ抵抗が組み込まれており、外部終端の必要がありません。

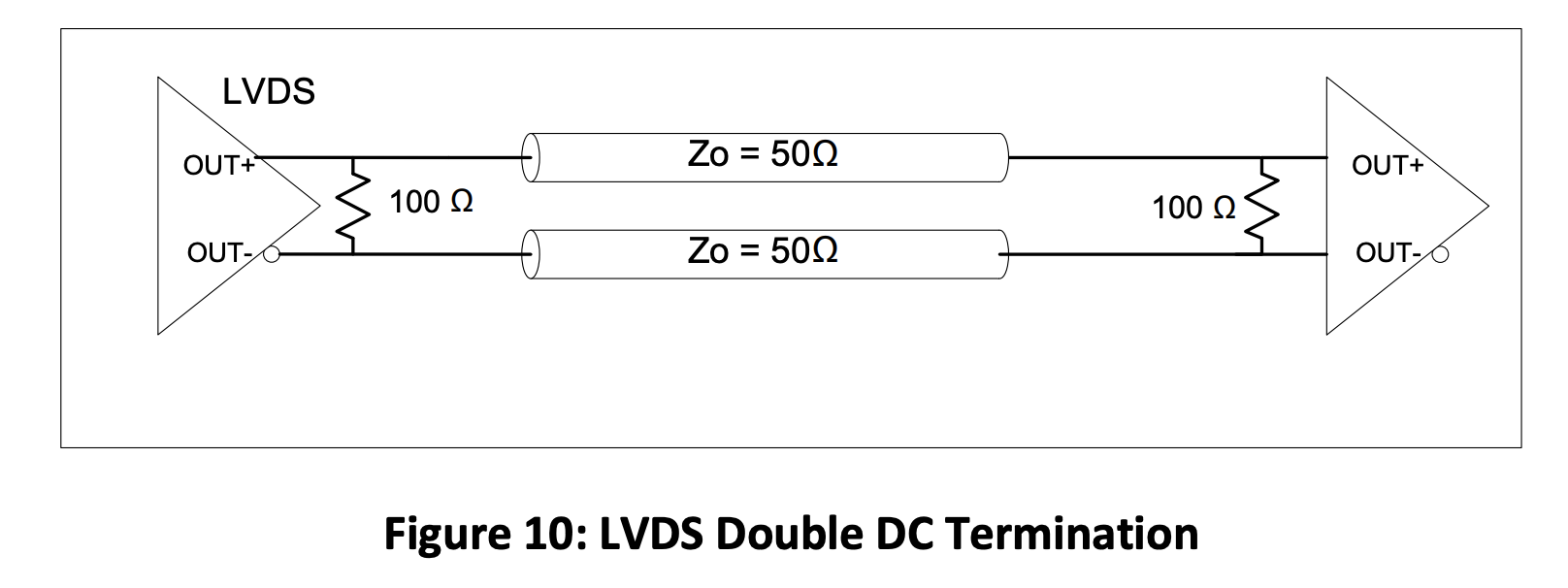

ほとんどのアプリケーションでは、負荷における単一の終端で十分です。負荷反射係数が比較的高い状況では、二重終端配置により全体のラウンドトリップが減少する可能性があります (図 10 を参照)。ソースと負荷の両方に 100Ω の抵抗があると、出力ドライバの等価抵抗は 50Ω に減少し、出力信号の振幅が半分になります。

3.2 AC結合アプリケーションの終端に関する推奨事項

LVDS ドライバとレシーバが異なるコモンモード電圧で動作している場合は、AC 終端を推奨します。コンデンサはドライバからの DC 電流経路をブロックするために使用されるため、レシーバは独自の入力バイアス回路を実装する必要があります。

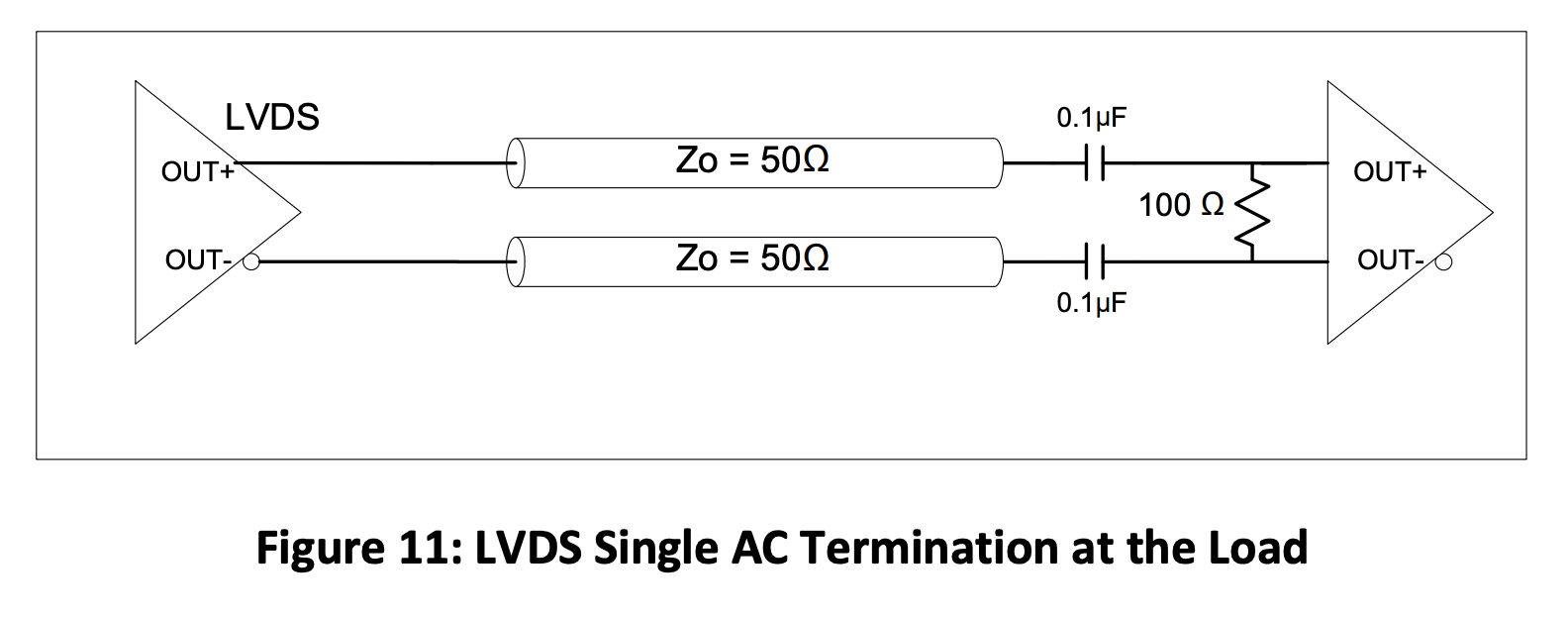

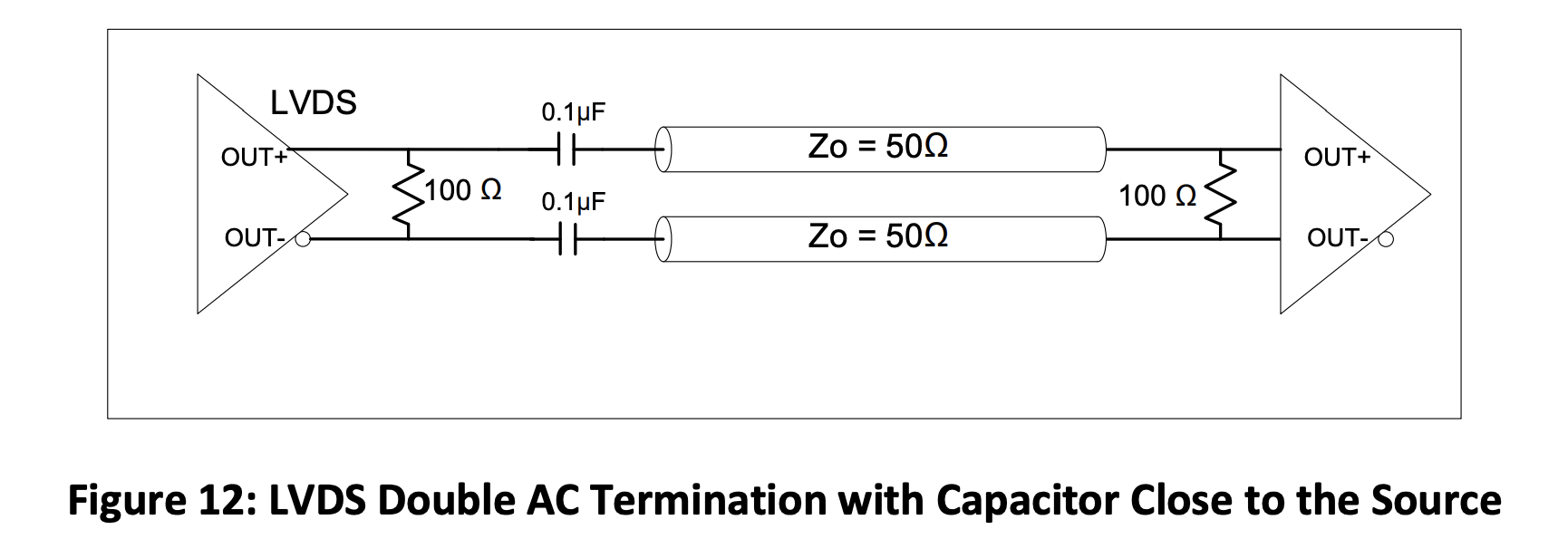

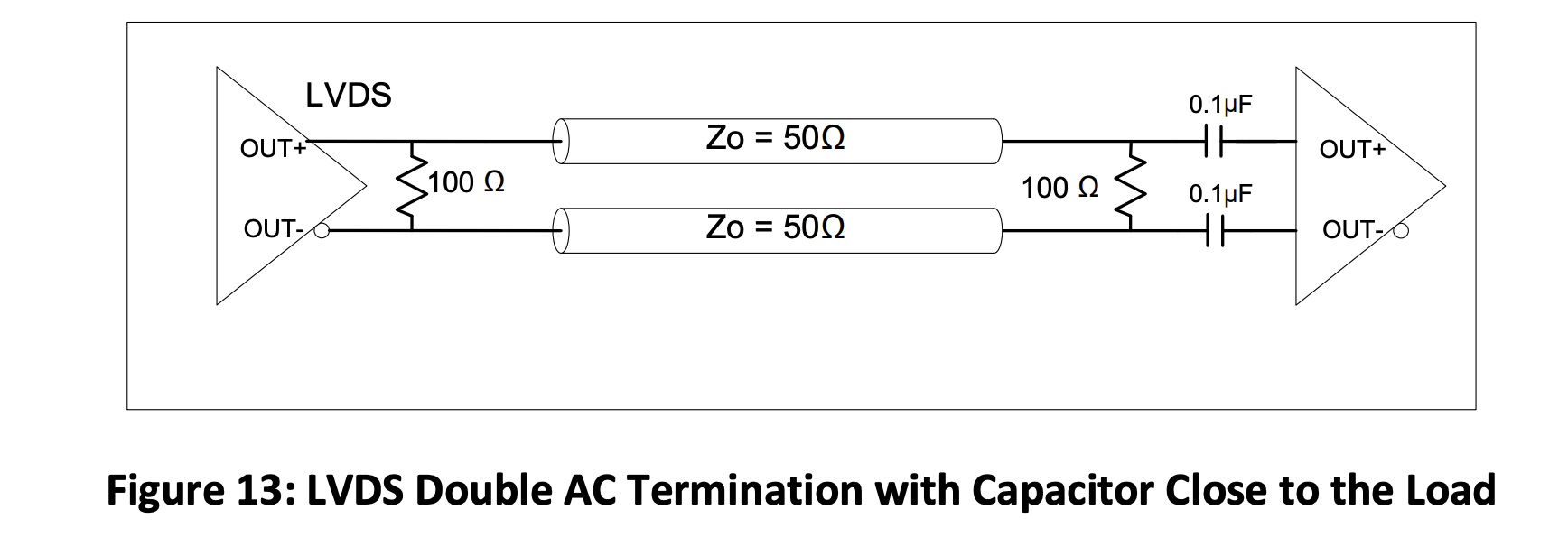

AC 結合は、負荷における単一終端または二重終端として構成できます。単一終端を図 11 に示します。単一終端と二重終端の両方で、AC カップリング コンデンサを負荷終端抵抗の前 (図 12 に示す) または後 (図 13 に示す) に配置できます。

(図 12 と図 13) に示す二重終端は、AC カップリング コンデンサの位置のみが異なります。図 12 のコンデンサは、微分抵抗の半分 (50Ω に相当) を流れるコモンモード電流によって充電されます。図 13 のコンデンサは、受信機入力の抵抗を流れる電流によって充電されます。この電流は数十キロオームの範囲になる場合があります。クロックの起動中、図 12 に示すコンデンサは、図 13 に示すコンデンサよりもはるかに速く充電されます。したがって、有効なクロック信号が受信機でより早く利用可能になります。高速クロック起動が重要な場合は、図 12 に示す構成が推奨されます。

データ送信アプリケーションでは、図 13 に示す構成の方が有利な場合があります。 RC 時定数が高いため、大きな電圧降下を経験することなく、より長い 1 と 0 のデータ シーケンスを維持できます。

4. HCSL出力

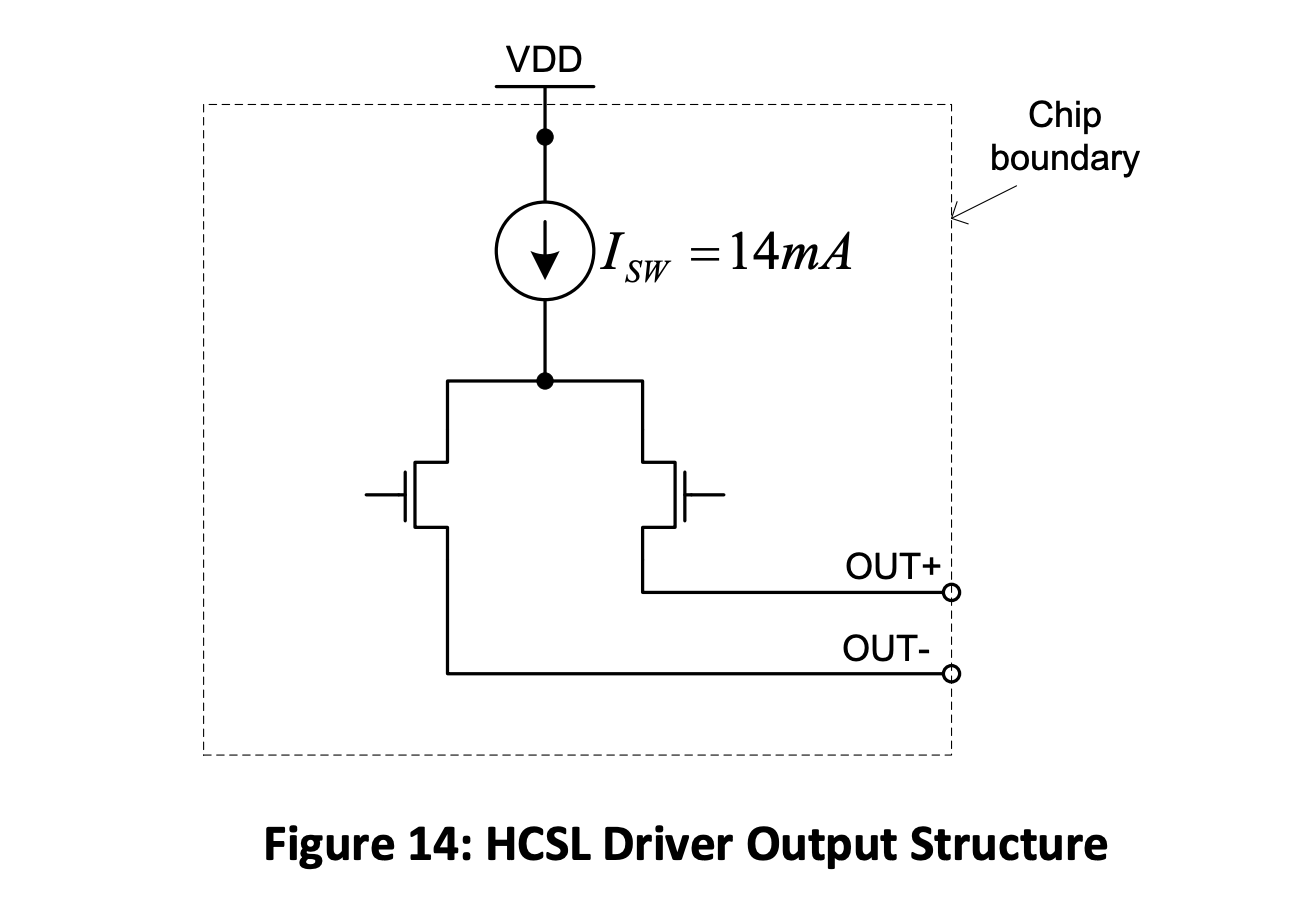

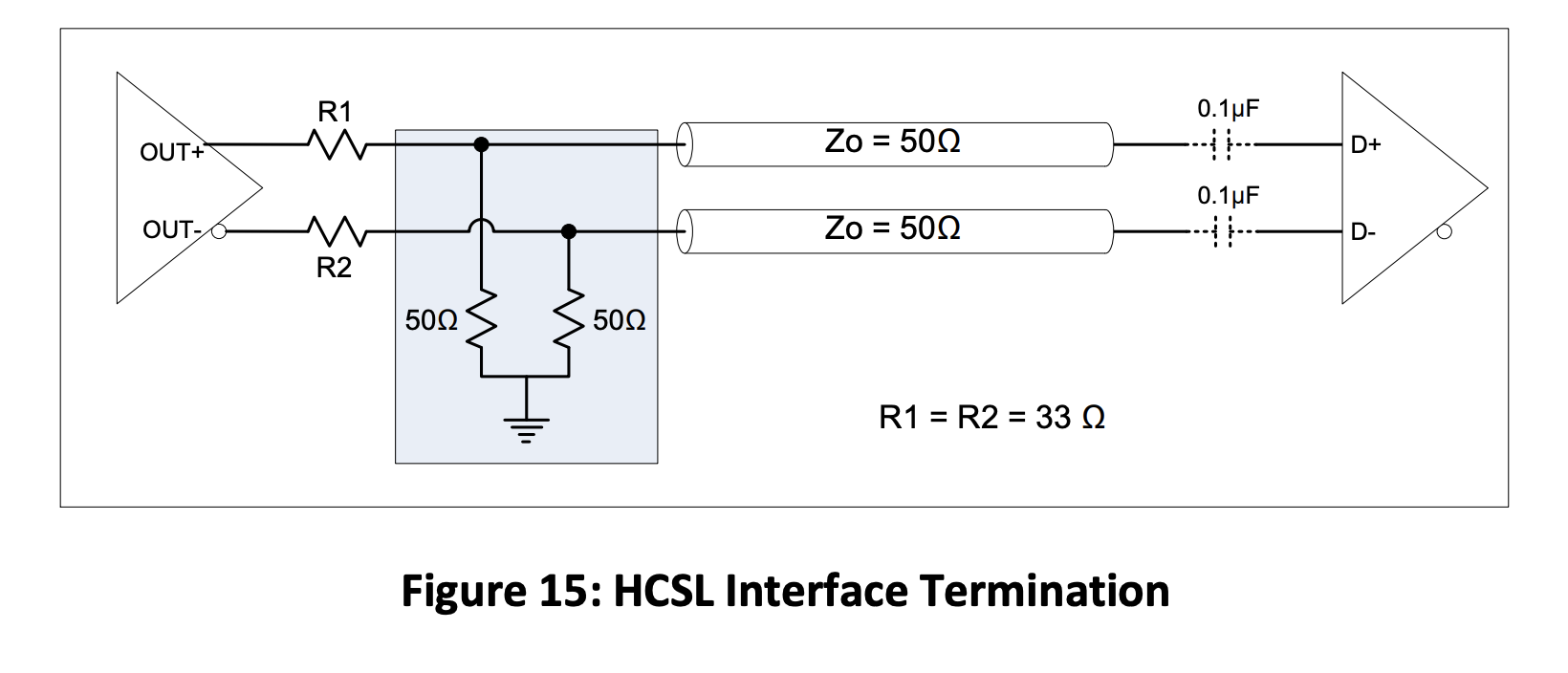

HCSL ドライバー オプションは、一部の SiTime オシレーター ファミリでのみ使用できます。 HCSL 出力構造 (図 16、図 14 を参照) は、図 15 に示すように、通常は 50Ω 抵抗を介してグランドに終端される 14 mA スイッチ電流源によって駆動されます。公称信号振幅は 700 mV です。出力のオープンドレイン トランジスタは、数キロオームの範囲でかなり高いインピーダンスを持っています。 AC の観点から見ると、出力トランジスタのインピーダンスは 50Ω の負荷抵抗と並列になり、等価抵抗は 50Ω に非常に近くなります。このインターフェースで使用される配線の特性インピーダンスは 50Ω であるため、負荷から反射された信号は発生源で吸収されます。通常、2 つの小さな抵抗 R1 と R2 (図 15 を参照) が高インピーダンス ドライバと直列に配置されます。これらは、出力からの電流の急激な上昇を遅らせることによってオーバーシュート リミッターとして機能し、ソースでのインピーダンス整合には影響を与えません。 SiTime では、これらの抵抗に 33Ω を推奨しています。

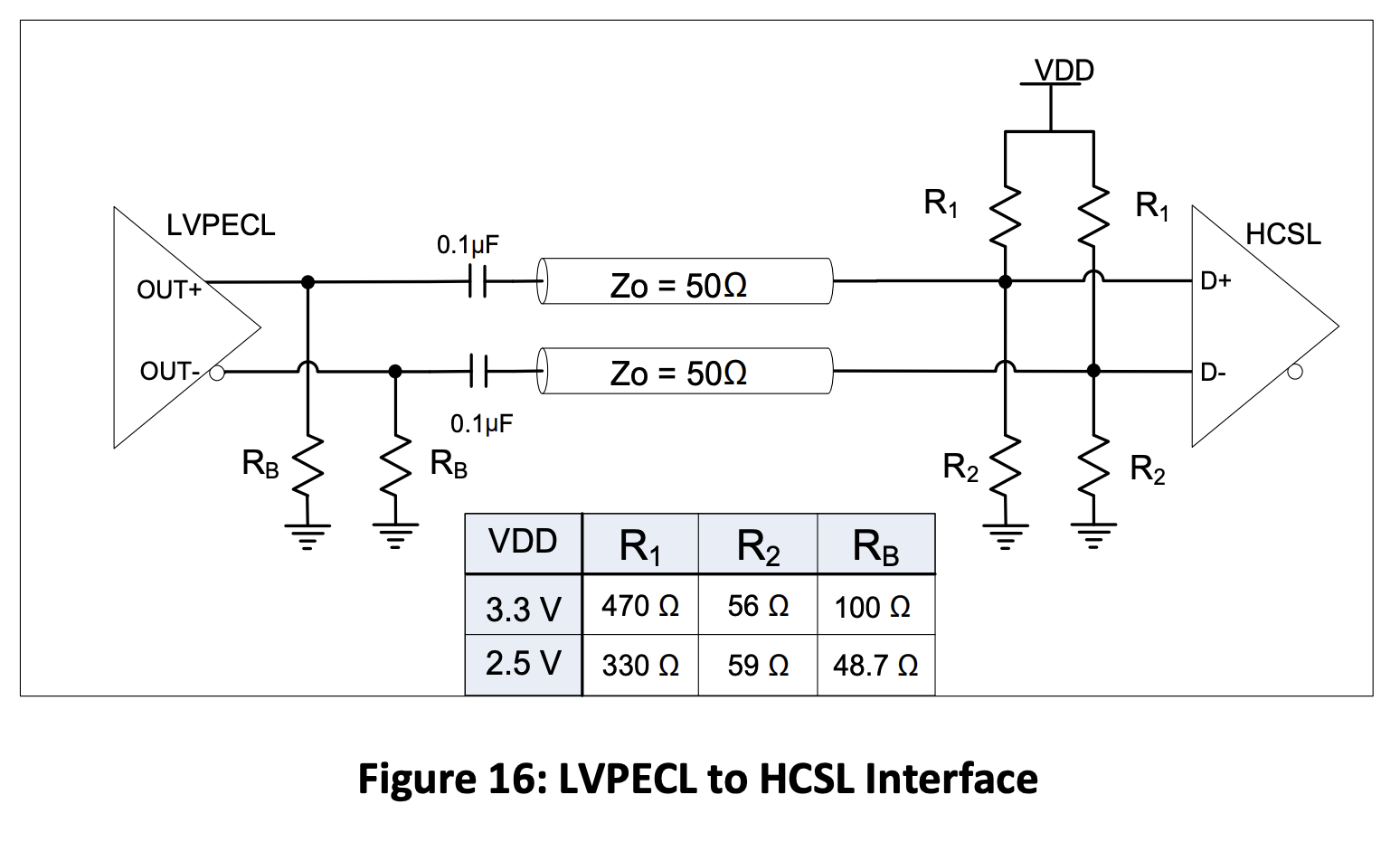

5. LVPECL 発振器を使用した HCSL レシーバーの駆動

一般的な HCSL インターフェイスは電流モード ドライバを利用し、ソースでは 50Ω から GND への終端を使用し、レシーバ側では終端を使用しません。さらに、HCSL 出力ドライバーの場合、LVPECL ドライバーを使用して HCSL 入力を駆動できます。図 16 に、LVPECL 出力で HCSL レシーバを駆動する場合の推奨終端回路図を示します。 HCSL受信機が要求する750mVのVOHレベルと0VのVOLレベルを満たすために、電源と負荷のバイアス電圧を分離するAC結合コンデンサを備えています。

負荷側のテブナン等価終端により、レシーバ入力に適切なコモンモード電圧も設定されます。抵抗 RB は、LVPECL ドライバに適切な DC バイアスを提供します。推奨される終端ネットワーク部品の値は、2.5V と 3.3V の両方の動作電圧について図 16 に示されています。

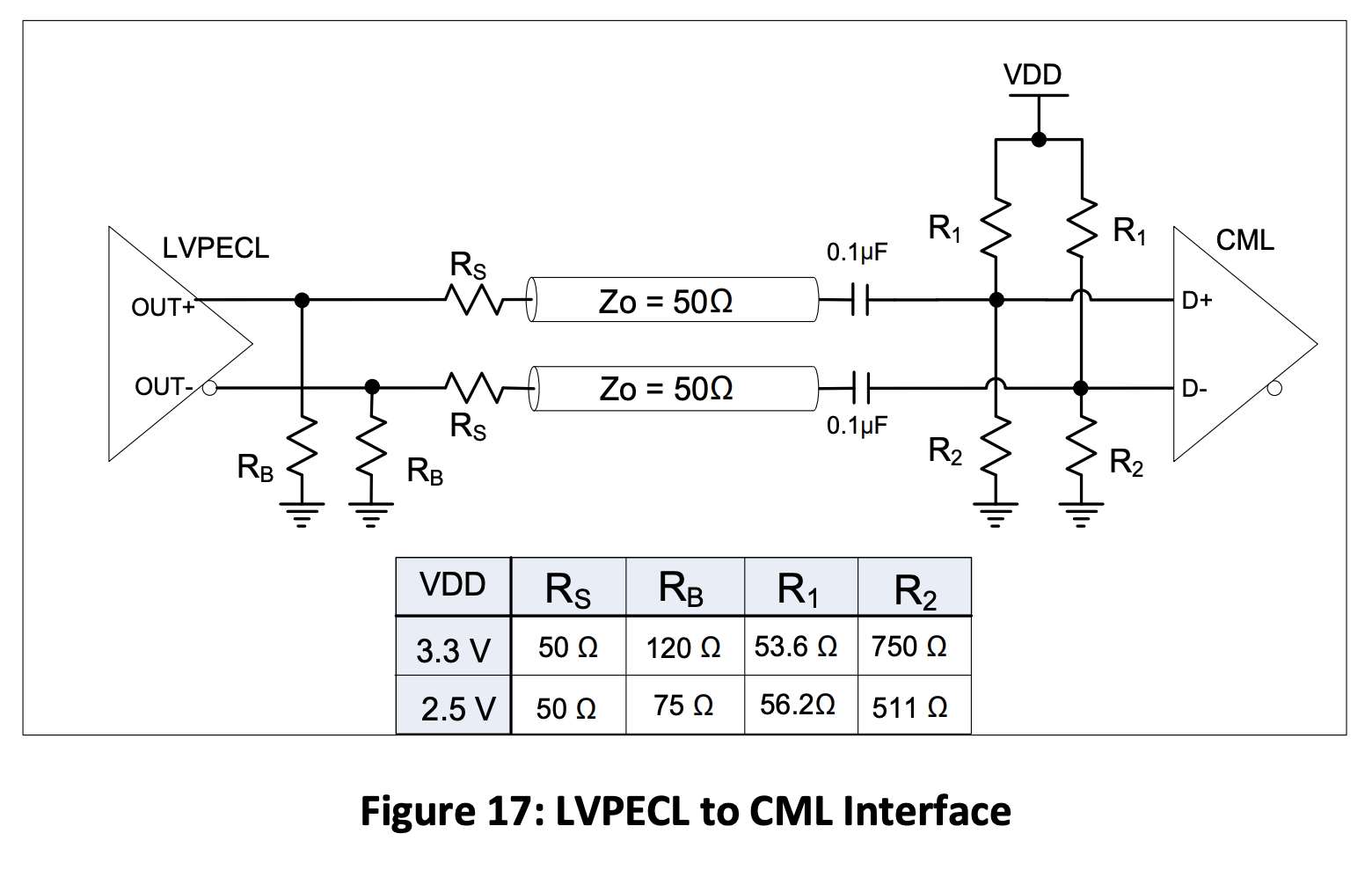

6. LVPECL 発振器を使用した CML レシーバーの駆動

ほとんどの SiTime 差動発振器には CML 出力オプションがありませんが、LVPECL ドライバを使用して CML レシーバを駆動するために使用できます。この場合、終端回路は、レシーバ入力での 400 mV のシングルエンド電圧振幅と VDD – 200 mV のコモンモード電圧を保証する必要があります [2]。図 17 に、LVPECL 出力で CML レシーバを駆動するための推奨終端回路図を示します。 LVPECL と CML のコモンモード電圧の差が大きいため、DC 電流絶縁用の AC カップリング コンデンサが必要です。抵抗 RB は、LVPECL ドライバを適切にバイアスするために使用されます。レシーバ側のテブナン等価終端により適切なバイアス電圧が設定され、RB 抵抗と合わせて適切な信号振幅が確保されます。

7. 自己バイアス差動入力の駆動

多くの差動レシーバーには、オンチップ DC バイアス回路や終端ネットワークが備わっています。この場合、発振器の出力は AC 結合する必要があります。外部バイアスが必要な場合は、受信デバイスのデータシートに従って設計する必要があります。

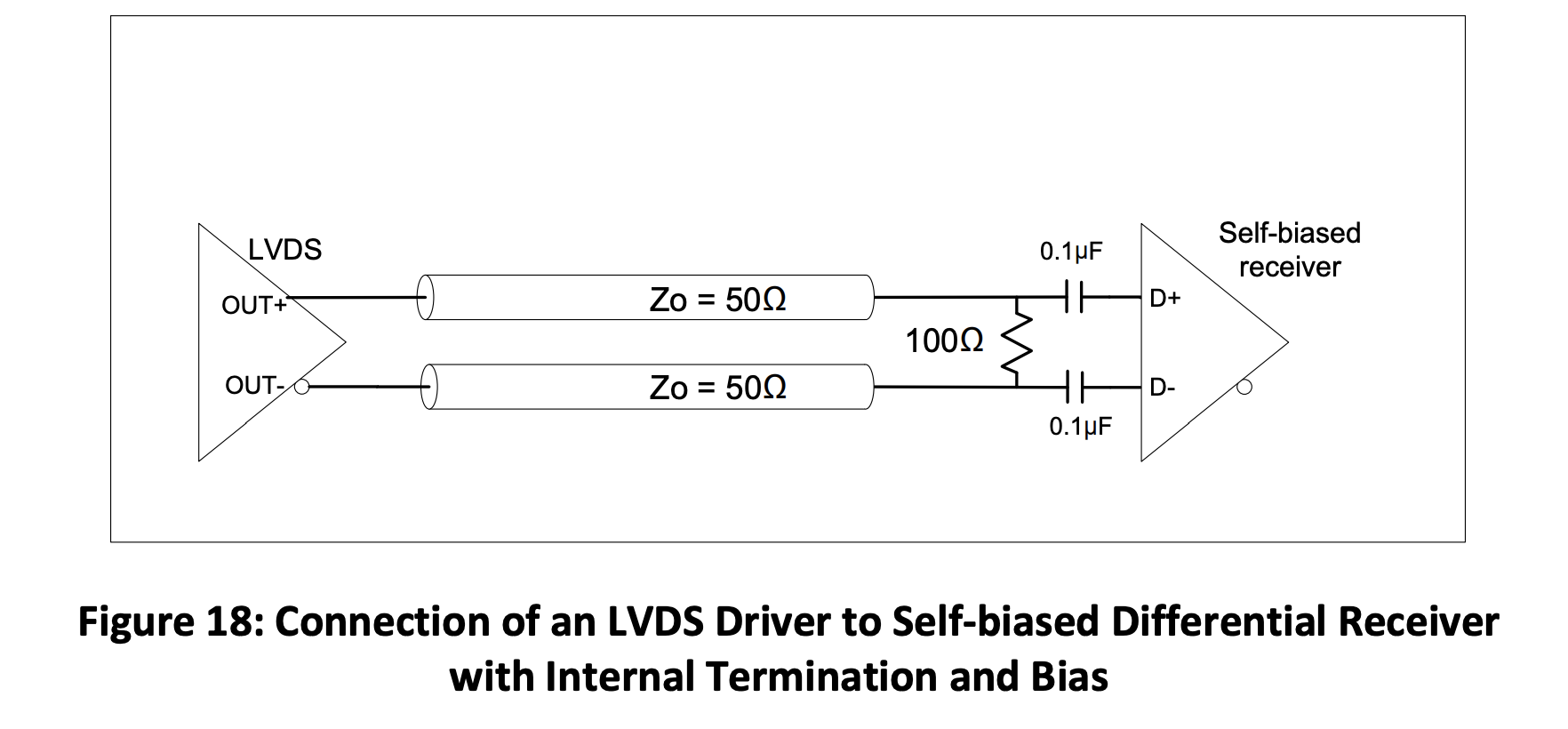

LVDS または LVPECL 発振器は、自己バイアス差動入力の駆動に使用できます。 LVDS 出力では、必要な受動部品が少なくなり、動作電力も低くなります。 700 mV の LVDS スイングがレシーバにとって十分な場合は、LVDS 発振器を使用することをお勧めします。図 18 は、LVDS 発振器と自己バイアス差動レシーバのインターフェイスを示しています。

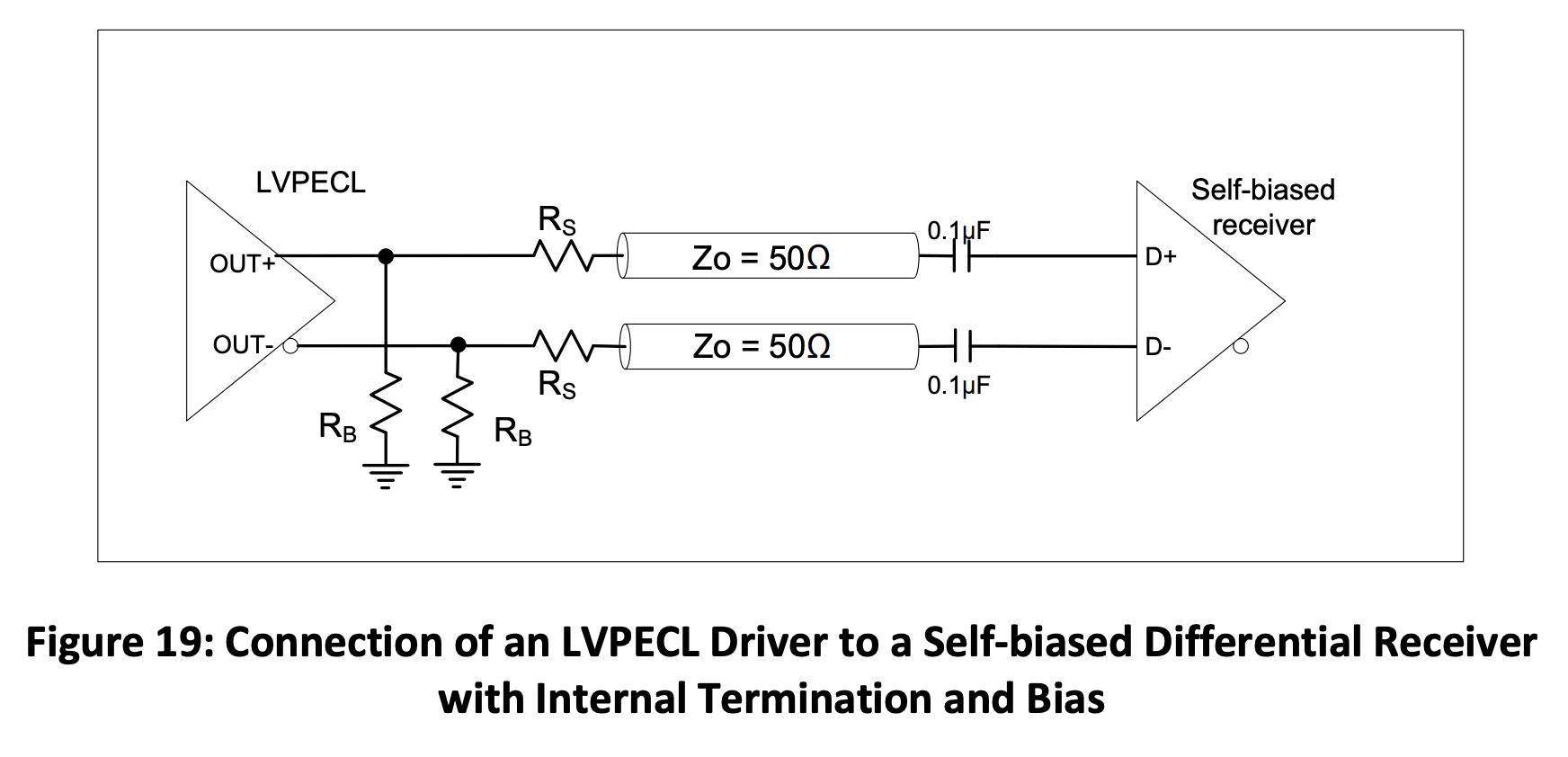

LVPECL 出力は、レシーバで最大 1.6V の差動スイングを生成できます。図 19 は、LVPECL 発振器を自己バイアス差動レシーバに接続するための回路図を示しています。抵抗 RS は、負荷側で終端する分圧器を作成します。受信機入力の電圧スイングは、RS 値を選択することで設定できます。 RB は LVPECL ドライバに DC バイアス電流を供給し、その値は式 1 から計算できます。レシーバでは実効終端抵抗値が RS + 50Ω になることに注意してください。

信号の完全性を維持するには、RS と RB を送信ラインの前の発振器にできるだけ近い位置に配置する必要があります。負荷側の終端ネットワークは、受信機入力のできるだけ近くに配置する必要があります。

8. LVPECL ドライバーを使用した LVDS レシーバーの駆動

LVDS レシーバは、LVPECL クロック信号で駆動できます。これには、受信側で信号を LVDS 信号要件内に収める終端技術を使用する必要があります。信号のコモンモード電圧と信号の振幅は、満たさなければならない主な仕様です。 LVDS 仕様を満たすには、LVPECL 信号の振幅を 1.6V から 0.75V に下げる必要があります。 LVPECL ドライバのコモンモード電圧は電源電圧に依存し、2.5V VDD の場合は LVDS コモンモード電圧と一致します。 2.5V LVPECL ドライバを使用して LVDS レシーバのクロックを可能にする終端を図 20 に示します。

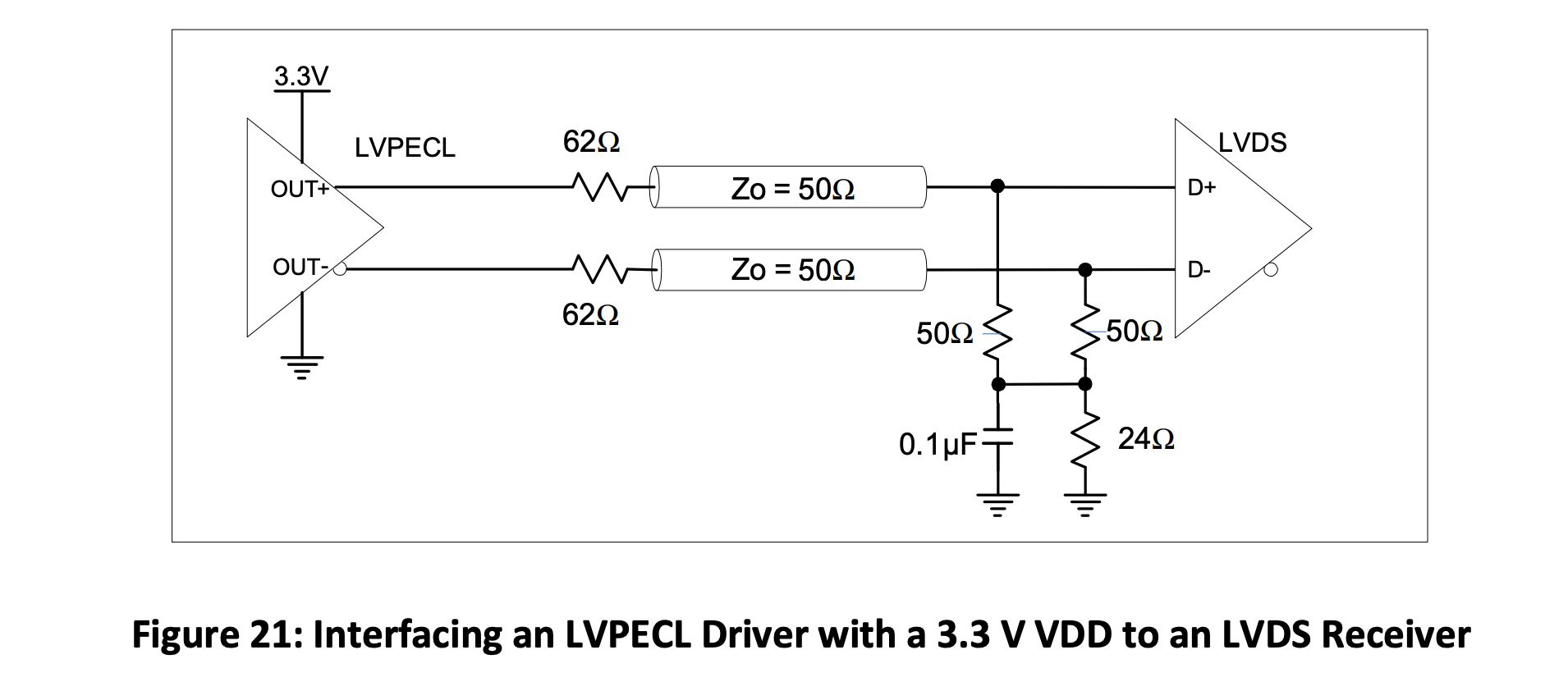

3.3V VDDの場合、LVPECLドライバとLVDSレシーバのコモンモード電圧は異なります。図 21 は、LVPECL ドライバと LVDS レシーバ間のインターフェイスとして直列抵抗と Y 終端を使用することを提案しています。

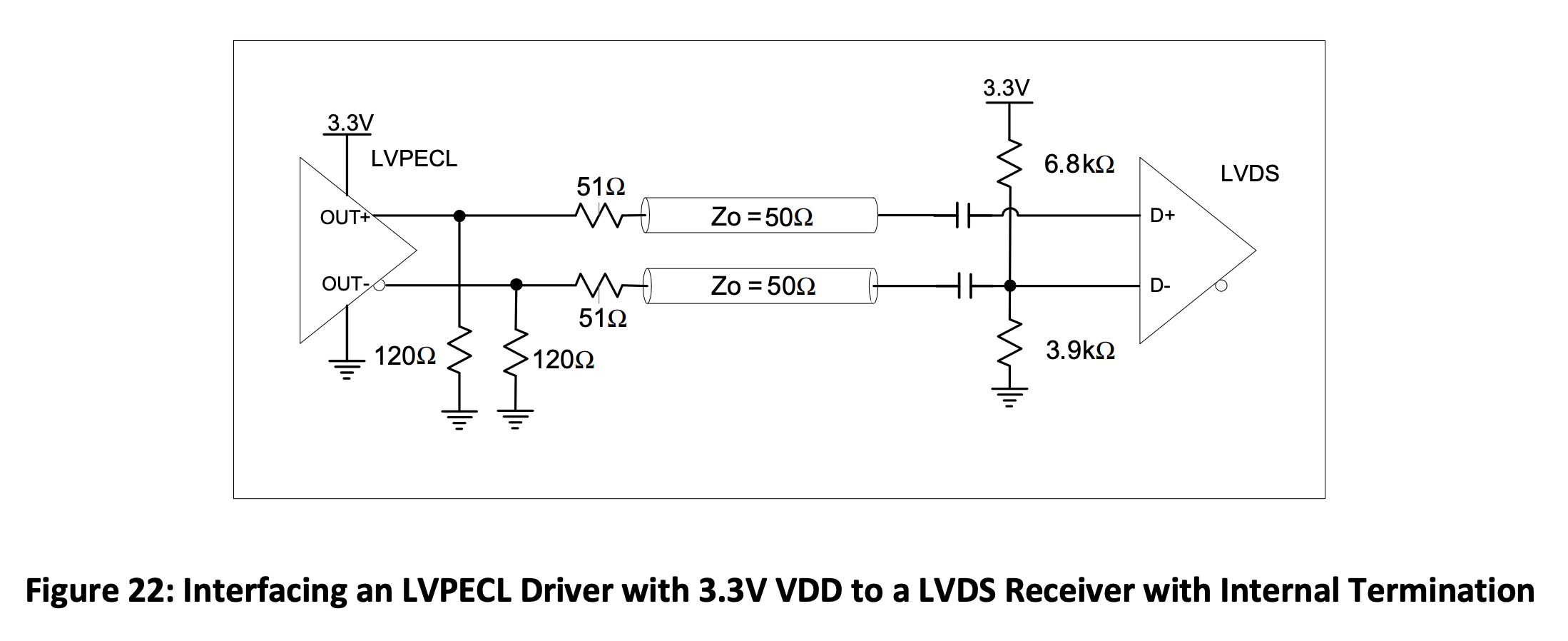

レシーバにオンチップ終端がある場合は、図 22 に示すように AC 結合を推奨します。コモンモードは抵抗分圧器によって設定されます。等価抵抗が高すぎて正入力と負入力の間で不均衡が生じるため、一方の入力のみがバイアスされます。

9. LVCMOS 発振器と LVDS/LVPECL 入力のインターフェイス

場合によっては、シングルエンド出力ソースを備えた差動 LVDS または LVPECL レシーバのクロッキングが必要になります。 LVCMOS 出力は、差動入力ピンの 1 つに AC 信号を接続し、もう 1 つのピンに DC しきい値電圧を適用することにより、LVDS または LVPECL レシーバに接続できます。差動スイングの要件を満たすには、レシーバー側のシングルエンド クロックの振幅が LVDS または LVPECL インターフェイスの差動スイングの 2 倍である必要があります。レシーバーのデータシートを参照して、入力電圧が許容範囲内であることを確認してください。

シングルエンド発振器で LVDS/LVPECL 入力を駆動すると、差動発振器と比較して消費電力が大幅に低くなりますが、ノイズ耐性が低下します。

シングルエンド出力を差動レシーバーにインターフェースするには、次の条件が必要です。

- 入力のコモンモード電圧は、すべての VDD で LVDS の場合は 1.2V、2.5V VDD での LVPECL の場合は 1.2V、3.3V VDD での LVPECL の場合は 2V である必要があります。

- 入力間の電圧振幅は、LVDS の場合は 700 mV ~ 800 mV、LVPECL の場合は 1.2 V ~ 2 V である必要があります。

- 信号の完全性を維持するには、終端回路の入力インピーダンスがトレース インピーダンスと一致する必要があります。標準的な配線インピーダンスは 50Ω です。

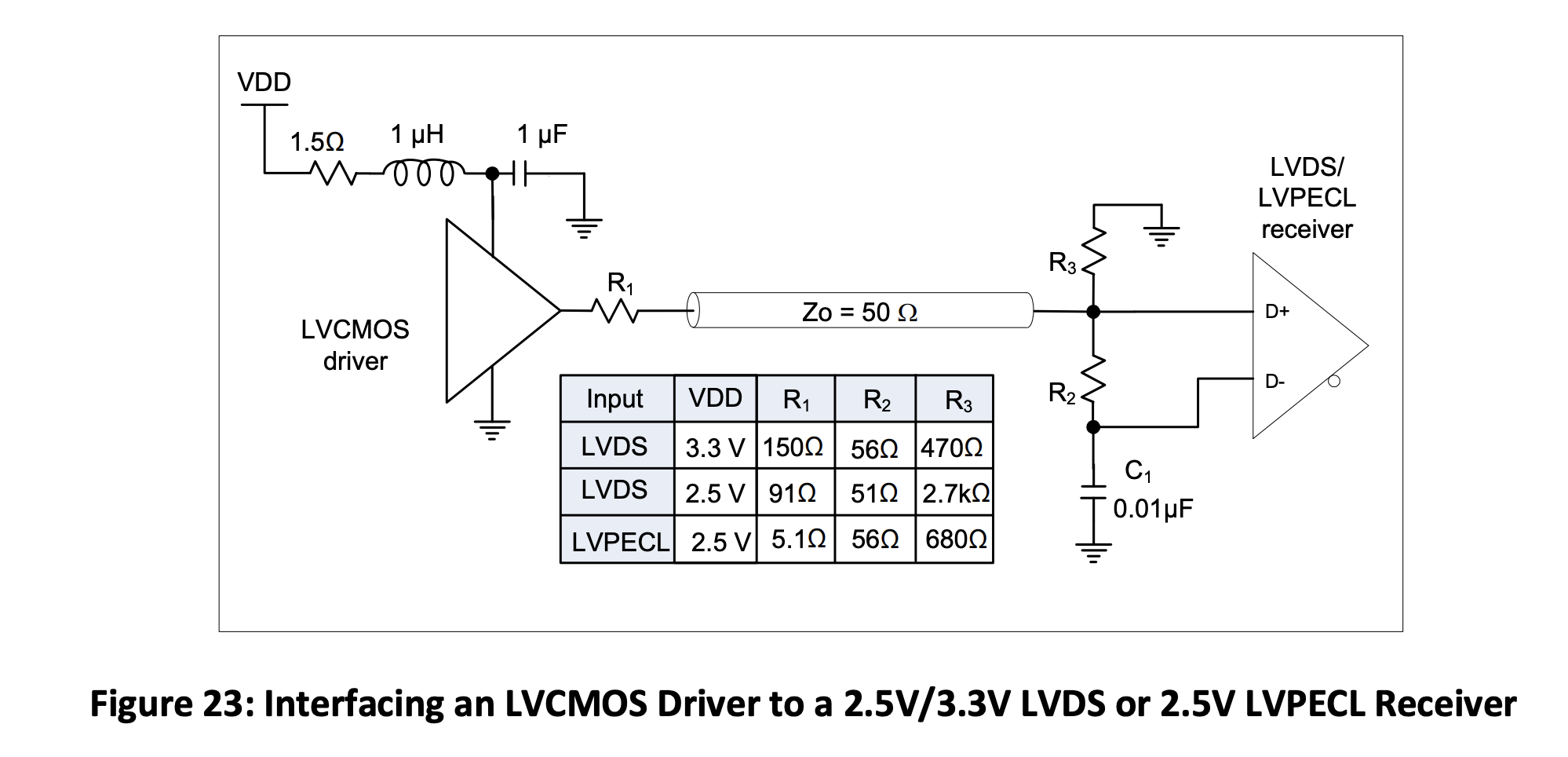

図 23 は、シングルエンド出力を 2.5V VDD の任意の電圧 LVDS および LVPECL にインターフェースするための推奨回路図を示しています。コモンモード電圧は、出力ドライバのインピーダンスと抵抗 R1 および R3 によって生成される分圧器によって設定されます。コンデンサ C1 は、負入力からグランドへの AC 信号経路を提供します。正入力の信号振幅は分圧器によって設定されます。分圧器は、R1 と直列の出力ドライバ抵抗、および R3 と並列の R2 で構成されます。

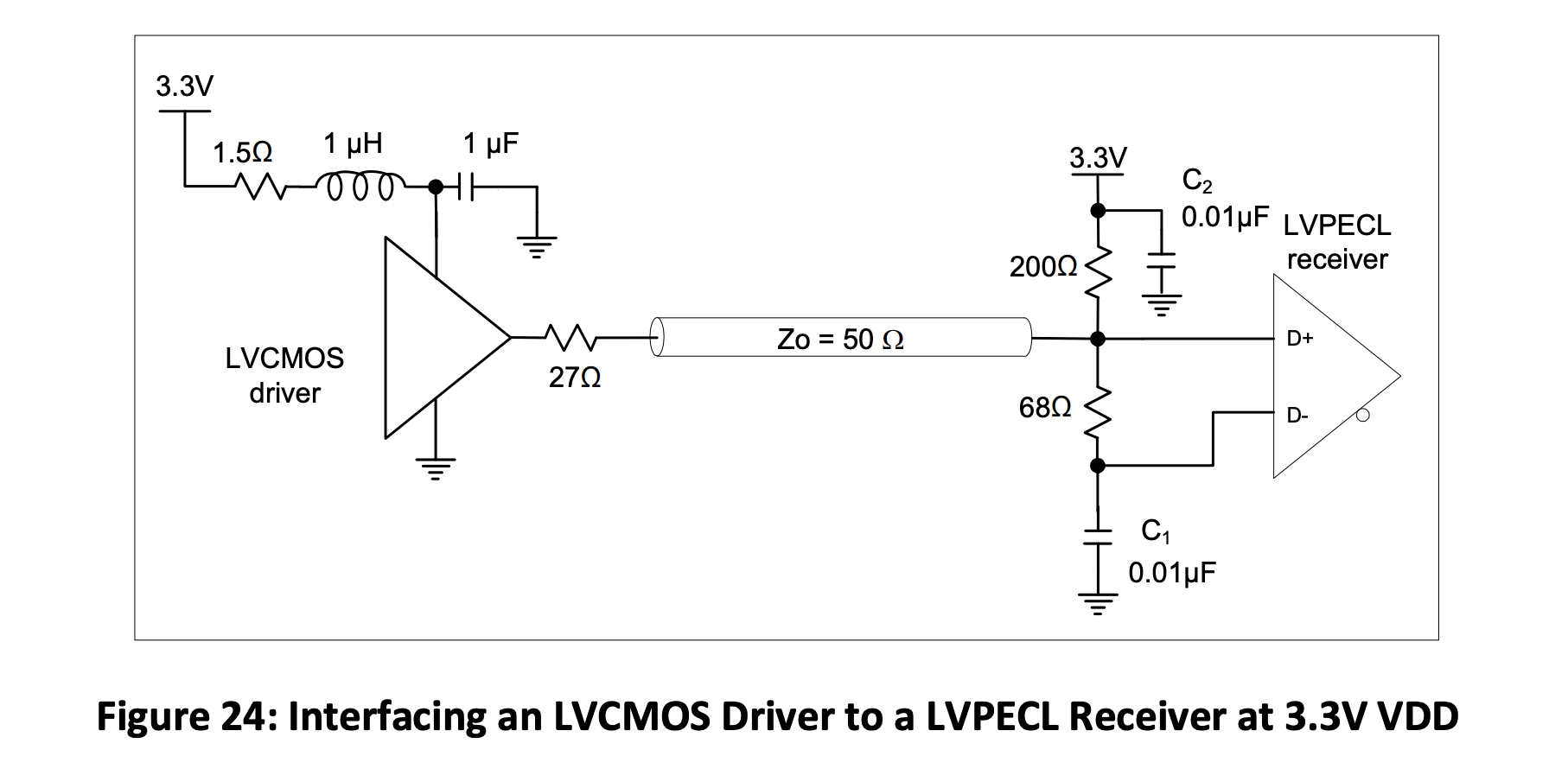

図 24 に、3.3V VDD での LVCMOS と LVPECL のインターフェース回路図を示します。レシーバ側のコモンモード電圧は、27Ωの抵抗とVDDへの200Ωのプルアップと直列に接続された出力ドライバのインピーダンスによって生成される分圧器によって設定されます。

図 23 および図 24 の推奨部品値は、25Ω LVCMOS ドライバ インピーダンスに基づいて計算されています。この値は、LVCMOS 発振器の SiT8008 ファミリの標準ドライバ インピーダンスに対応します。

図 23 と図 24 に示すように、LVCMOS 発振器の電源ネットワークには RLC フィルタがあります。SiTime では、電源ノイズ除去が大幅に改善されるため、この RLC フィルタの使用を推奨します。

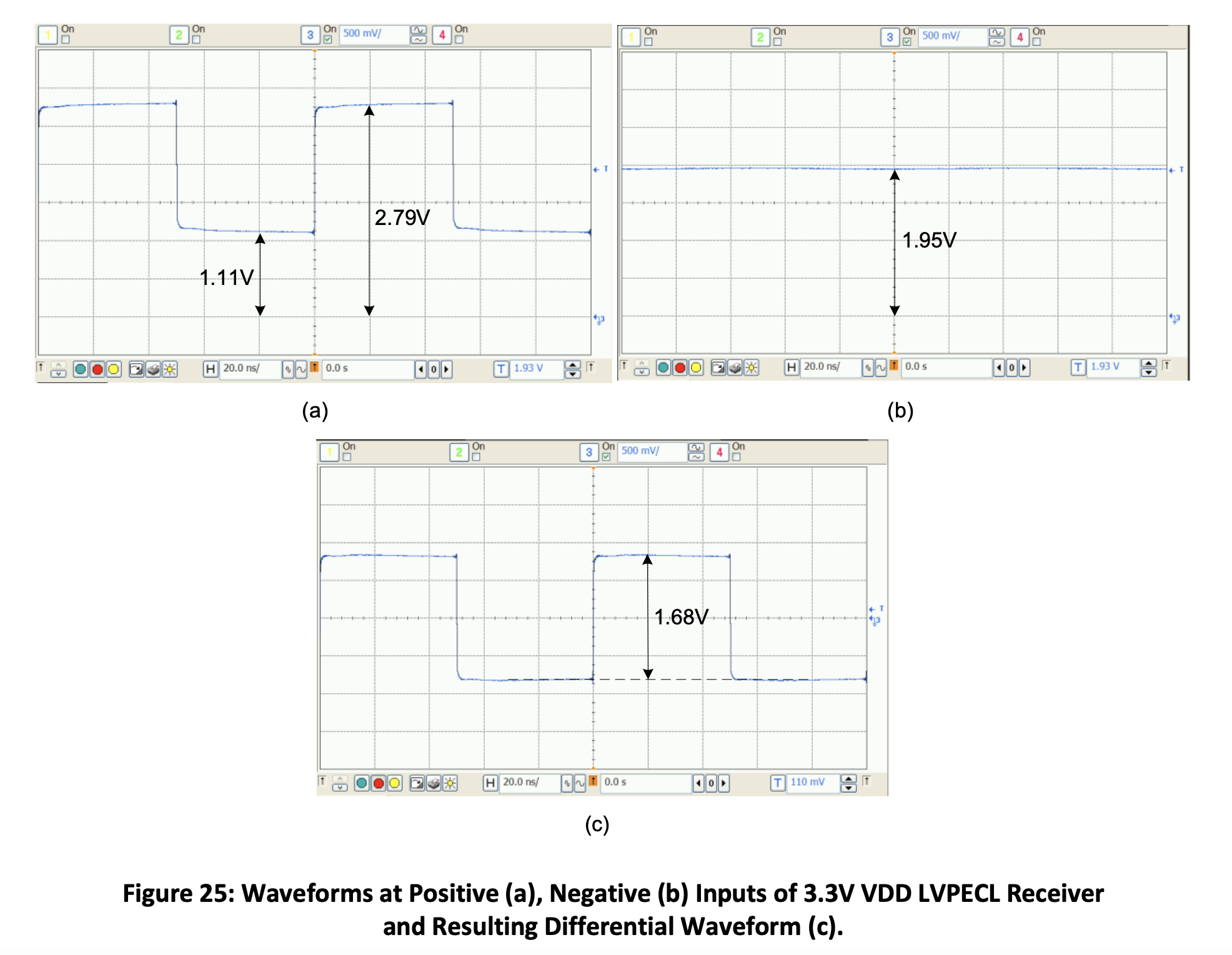

図 25 に、シングルエンド クロックで駆動した場合の 3.3V LVPECL レシーバの入力波形の例を示します。

10. 結論

このアプリケーション ノートでは、SiTime 差動発振器の出力ドライバ構造と、LVPECL、LVDS、および HCSL 差動出力で最も一般的に使用される AC 結合および DC 結合終端方式について説明します。 LVPECL 出力を使用して HCSL および CML レシーバーに接続するための推奨オプションについて説明します。シングルエンド LVCMOS 発振器を使用して LVDS または LVPECL クロック レシーバを駆動できるようにする終端方式も紹介されています。出力タイプの幅広い選択肢により、ユーザーは要件に最適な出力信号を選択できます。

このアプリケーション ノート [AN10029] の PDF をダウンロードしたい場合は、 ここをクリックしてください。付録 A は PDF に含まれています。

改訂履歴表

バージョン | 発売日 | 変更の概要 |

1.0 | 20013/04/30 | オリジナルのドキュメント。 |

2.0 | 2013/11/01 | わかりやすくするために編集します。 追加セクション: LVPECL ドライブを使用した LVDS レシーバーの駆動 セクションを追加: LVCMOS 発振器を LVDS/LVPECL 入力に接続する |

2.1 | 2018/06/19 | ドキュメントが再構成され、新しいページ レイアウトが適用され、更新されたロゴと新しい会社住所が適用されました。 わかりやすくするために編集します。 セクション 4: HCSL 出力を追加。 SiTime 発振器のリストが現在の製品ラインを反映するように更新され、表 1 に移動されました。 |