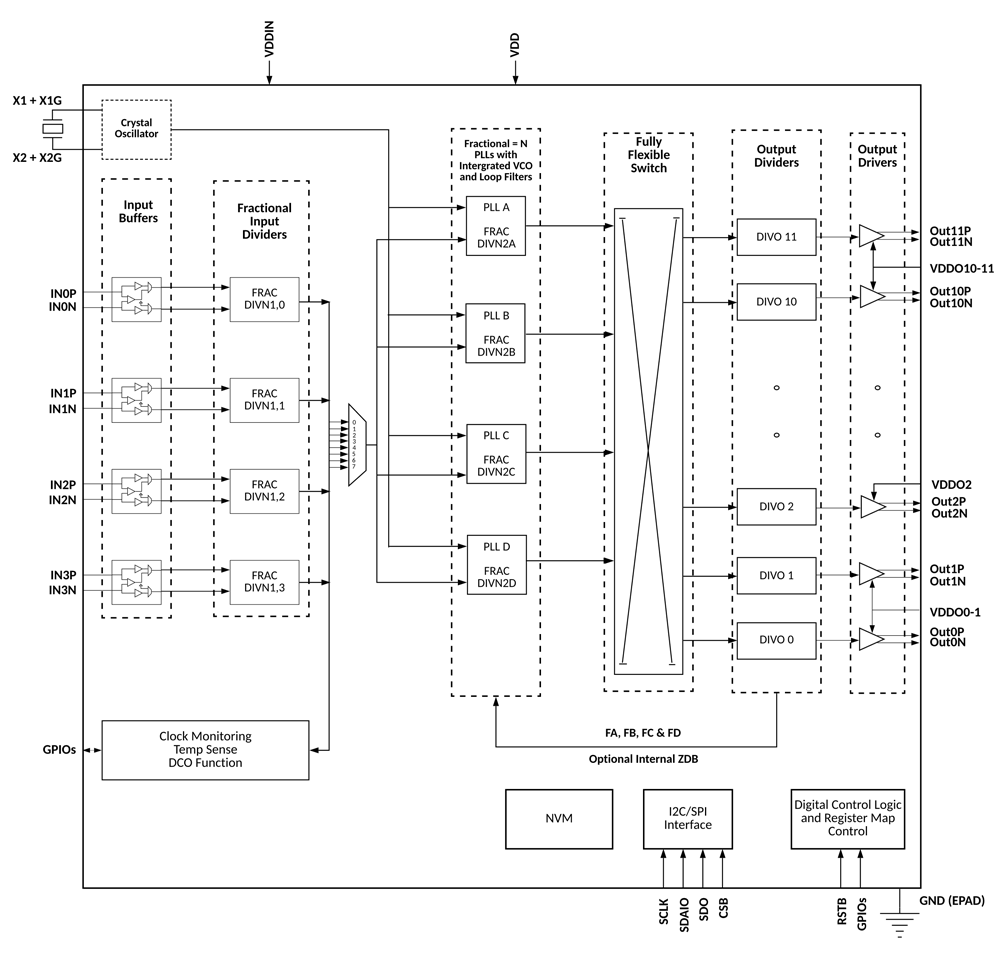

SiT95211 は、柔軟な入力から出力への周波数変換オプションを備えたプログラム可能なクワッド フラクショナル周波数生成および変換を提供します。超高ジッタ性能の DPLL は、4 つのフラクショナル PLL すべてに共通する最大 4 つの差動またはシングルエンド入力クロックをサポートし、12 の差動出力クロックを提供します。クロック出力は、4 つの PLL のいずれかから完全に柔軟な方法で生成できます。このデバイスは、I2C/SPI インターフェイスまたは工場で事前プログラムされたデバイス用のオンチップのワンタイム プログラマブル不揮発性メモリを使用して完全にプログラム可能です。

- 位相ノイズが低いため、ビットエラー率が最小限に抑えられ、56G/112G PAM4 I/O システムの設計マージンが向上します。

- 信号整合性が向上すると設計マージンが拡大し、市場投入までの時間が短縮されます。

- クロックツリーの統合度が上がると、システムBOMが削減され、全体的な信頼性が向上します。

| "スペック" | "値" |

|---|---|

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 9x9 mm, 64-pin QFN |

| Number of Inputs | 4 |

| Number of Outputs | 12 |

| Input Type | LVCMOS, LVDS, LVPECL, CML |

| Input Frequency Range | 200 kHz to 2.1 GHz (Differential) |

| Output Type | LVPECL, CML, HCSL, LVDS, LVCMOS |

| Output Frequency Range | 0.5 Hz to 2.94912 GHz (Differential) |

| Number of PLL/Clock Domains | 4 PLL |

| Phase Jitter (rms) | 85 fs typ.; 70 fs typ. (with MEMS oscillator) |

| Repeatable Input-Output Delay | ±225 ps |

| Frequency Control DCO | 0.001 ppt (all outputs) |

| Phase Control DCO | <1 ps (all outputs) |

| Internal ZDB Mode | <0.5 ns Input to Output delay variation |

| Programmability | NVM OTP, External EEPROM, Partial autonomous, SPI/I2C |

| Features | Independent output supply pins: 3.3 V, 2.5 V, or 1.8 V |

| Availability | Production |

-

64-pin 9x9 mm QFN Clock Generators - Network Synchronizers - Jitter Cleaners package

- クラス最高の 85 fs / 70 fs 統合ジッタ、Quad PLL 用

- データコンバータクロックのJESD204B/Cサポート

- 外部EEPROMサポートとオンチップOTP

- 周波数 DCO (0.001ppt) および位相制御 DCO ( 1ps 分解能)

- すべてのPLLに内部ZDBを搭載し、温度範囲全体で入力から出力までの遅延が+/- 500 ps未満

- 独立したVDDO(3.3 / 2.5 / 1.8 V)

- 出力は独立した同期パルスで位相調整可能

- イーサネット

- フレーマー、マッパー、プロセッサー向けの光トランスポート ネットワーク (OTN) クロッキング

- マイクロ波バックホール

- 100G / 200G / 400G / 800G イーサネット

- ワイヤレスネットワーク

- スモールセル

- ストレージ、サーバー、データセンター

- SONET/SDH ストラタム 3

- テストと測定

- ブロードキャストビデオ

SiT95211 評価ボード HW ユーザーマニュアル–デバイスのパフォーマンスの設定と評価

SiTGUI 3.6.1.1 のセットアップ– ソフトウェア .exe ファイルのダウンロード

Apply Filters

| Resource Name | Resource Type | Date | Format | Size |

|---|