従来のタイミングデバイスの限界を克服

従来のクロック ジェネレーターは、クロック生成の入力リファレンスとして、水晶ベースの発振器または共振器を使用します。MEMS 共振器を統合することで、Chorus ™クロック ジェネレーターは水晶への依存を排除し、水晶に関連するパフォーマンスと信頼性の問題も解消します。Chorus は、データセンター、AI、コア/エッジ/アクセス ネットワーク アプリケーションに MEMS とシステム統合の利点をもたらします。

| デバイス* | データシート | 差額の回数 出力 | LVCMOSの数 出力 | 頻度 安定性 | RMSジッター (タイプ) | 頻度 | サイズ (QFN) |

|---|---|---|---|---|---|---|---|

| SiT91211 | 4 | 8 | ±20 または ±50 ppm | 150fs | 1~700MHz | 4 x 4mm | |

| SiT91213 | 4 | 8 | ±20 または ±50 ppm | 70fs | 1~700MHz | 4 x 4mm |

コーラス クロック ジェネレーターは、低電力、低ジッターのアプリケーション向けに設計されています。これらの柔軟なクロックには、設定可能な出力周波数、出力バッファ タイプ、出力スキュー制御、電源電圧、および特定の設計要件を満たすその他のプログラム可能な機能が備わっています。

- 低 RMS 位相ジッタ: 70 fs または 150 fs (通常) (12 kHz ~ 20 MHz)

- 柔軟な周波数: 1 MHz から 700 MHz までプログラム可能な周波数

- 優れた周波数安定性: -40°C ~ 105°C で ±20 ppm および ±50 ppm

- 柔軟な供給電圧: プログラム可能、1.8V、2.5V、または3.3V

- 柔軟な出力タイプ: 最大4つの差動出力(LVPECL、LVDS、LPHCSL)または8つのLVCMOS出力、またはそれぞれの組み合わせ

- 消費電力の削減と回路の簡素化:FlexSwing™出力により消費電力が削減され、終端抵抗が不要になります。

- EMI低減: 設定可能なスペクトラム拡散クロック生成

- 優れた電源ノイズ除去(PSNR) : 0.01 ps/mv

- 最新のPCIe規格に準拠:第1~6世代

Chorus MEMS ベースのクロック ジェネレーターは、完全なクロック システム オン チップ (ClkSoC) です。クロック生成の入力リファレンスとして水晶に依存する従来のクロック デバイスとは異なり、Chorus クロックには統合型 MEMS 共振器が組み込まれています。高信頼性通信およびエンタープライズ アプリケーション向けに最適化されており、MEMS タイミングの利点を AI、データセンター、400G/800G/1.6TB 接続 (イーサネット、InfiniBand) にまで拡張します。

完全に統合されたソリューション

Chorus クロック ジェネレータは、シリコン MEMS 共振器と PLL テクノロジを組み合わせたシングル チップ ソリューションを提供します。これにより、システム クロック アーキテクチャが簡素化され、BOM が削減され、設計時間が最大 6 週間短縮されます。クロック IC 内に SiTime の実績ある MEMS 共振器テクノロジを統合することで、外部水晶振動子への依存がなくなり、容量不一致、アクティビティ ディップ、衝撃、振動、EMI に対する感受性など、外部水晶振動子に関連するすべての問題も解消されます。設計者は、クロック IC の出力周波数の不正確さの原因となる適切な水晶発振器回路と負荷容量の不一致を確認するために、複数の設計およびテスト サイクルを心配する必要がなくなります。

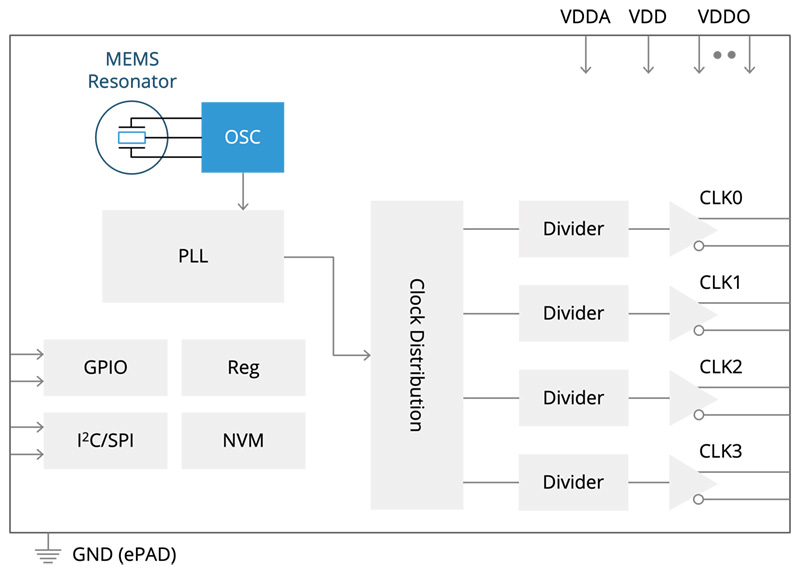

MEMS 共振器を統合した Chorus SiT91211/13 クロック ジェネレータのブロック図

Chorus クロック ジェネレータ アーキテクチャの主な要素は次のとおりです。

- 統合されたMEMS共振器と発振回路

- 完全にプログラム可能な低ノイズPLL

- 4つの整数分周器が高性能、低ジッタ出力を生成

- プログラム可能な低スキュークロック出力(それぞれに専用の電源が付属)(最大 4 つの差動または 8 つのシングルエンド)

- オンチップNVMは高い柔軟性を実現し、複数の構成をサポートして、現場でのクロックツリーの変更に対応します。

- オンチップレギュレータは優れた電源ノイズ除去(PSNR)を提供し、ノイズの多い状況でも低ジッタを保証します。

- GPIOピンを介した複数の内部パラメータのチップステータス監視、またはI2C/SPIを介した内部レジスタへの直接アクセス

フットプリントが50%小さくなりました

システムがより多くの機能を小さなスペースに詰め込むようになるにつれ、ボード スペースは常に貴重になります。従来のクロック ツリー設計では、通常、外部の水晶共振器 (クリスタル) または個別の発振器によって駆動されるクロック IC を使用します。対照的に、シングル チップの Chorus クロック ジェネレータ (内部に MEMS 共振器と発振器回路を搭載) は、外部共振器の必要性を排除するか、最大 4 つの発振器を置き換えることができます。コンパクトな 4 mm x 4 mm パッケージにより、クロック ツリー全体のフットプリントを最大 50% 縮小できます。

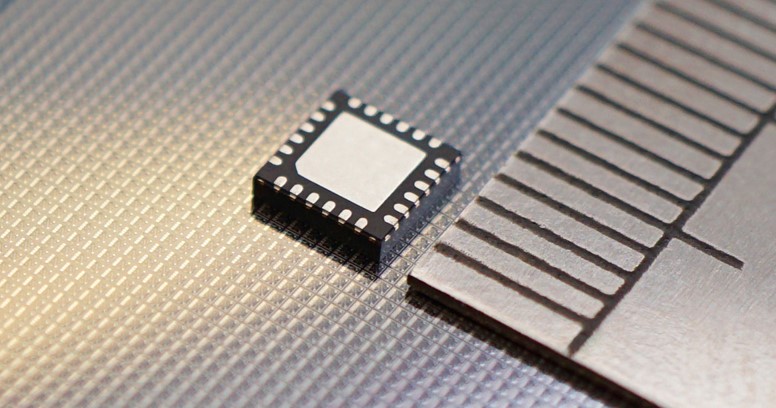

業界標準の 24 ピン 4 mm x 4 mm x 0.5 mm ピッチ (ウェッタブル フランク) QFN パッケージの Chorus SiT91211/13 クロック ジェネレーター

10倍の信頼性

従来のクロック IC は、入力クロック リファレンスとして水晶振動子を必要とします。この依存性により、システムの信頼性、設計、パフォーマンスに多くの問題が生じます。対照的に、Chorus クロック ジェネレーターは、現場で故障しやすい水晶振動子リファレンスを必要としません。SiTime の高品質と信頼性は、30 億ユニットを超える出荷で実証されており、故障率は 1 DPPM 未満、MTBF は 10 億時間を超えています。この信頼性は半導体業界でも最高レベルであり、水晶振動子よりも桁違いに優れています。

10倍の耐久性

コーラス クロックは、統合型 MEMS 共振器を備えており、水晶リファレンスに依存する従来のクロック ジェネレータの制限に対処します。外部水晶コンポーネントを使用して PCB を設計すると、敏感なアナログ ノードが露出し、EMI とボード ノイズが発振回路に結合する経路となります。このような結合を最小限に抑えるには、適切な PCB 設計が必要です。コーラス クロックは、クラス最高の 0.01 ps/mV の電源ノイズ除去を備えており、EMI によるノイズやシステム パフォーマンスの低下などの問題を排除します。さらに、コーラス クロックにはアクティビティ ディップ (周波数ジャンプ) がなく、機械的な衝撃や振動の影響をほとんど受けず、ボードの曲がりに対する脆弱性も大幅に低減します。

主要なリソース

コーラス クロック ジェネレーターに関するよくある質問

コーラス評価委員会

SiTime、AIデータセンター向け統合クロックチップで高精度タイミングの進化を継続