FPGA は、汎用 I/O を備えたオリジナルのロジックとフリップフロップベースのファブリックをはるかに超えて進化しました。最新の FPGA は、組み込みメモリ、DSP ブロック、 AIプロセッサ、および高速相互接続用のネットワークオンチップを統合しています。また、多くの FPGA はマルチコア プロセッサを搭載しており、 AI/ ML ワークロード向けに最適化されていることがよくあります。

I/O リングも進化し、ハード IP ブロックと高速 SerDes を組み込んで、ギガビット イーサネット、PCIe、DDR メモリなどのインターフェイスをサポートします。これらの追加により、最新の FPGA でますます複雑化するクロッキング要件に対応できます。

FPGAは複雑なクロック環境を表す

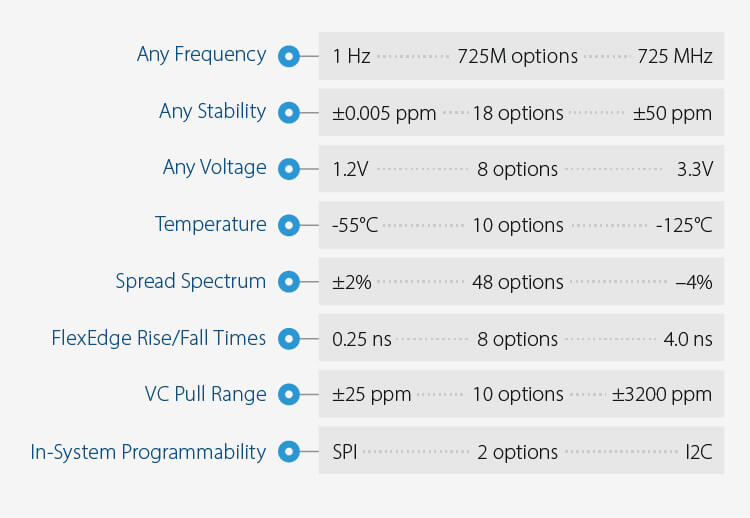

FPGA の機能が拡張されたことで、クロッキング要件がより複雑になりました。これらの要求に対応するために、FPGA ベンダーは複数の PLL とクロック管理機能を統合し、次のような多様なクロック ソースの需要を促進しています。

- 厳しい位相ノイズ要件を持つ SerDes トランシーバー用のリファレンス クロック

- RTC、IEEE 1588、GNSSベースのアプリケーションの計時とタイムスタンプ

- 組み込みPLL用の複数のリファレンスクロック

- I/Oバンクごとのリファレンスクロック

- ユーザーロジックのクロック

- 構成コントローラ、低速インターフェース、およびその他のシステム機能のクロックソースをサポート

SRAM ベースの FPGA では、通常、それぞれ独自のクロック ソースを持つ小さな CPU とフラッシュ メモリを使用して、構成に外部ロジックが必要になることがあります。

FPGA とその構成ロジックは、それぞれ異なるクロッキング ニーズを持つ高性能 CPU、FPGA ベースのアクセラレータ、トランシーバ、DRAM、およびその他の ASSP とともに動作します。これにより複雑なタイミング環境が生まれ、発振器から高度なクロック管理デバイスまで、幅広いクロッキング ソリューションを提供するサプライヤが必要になります。

FPGAはどこにでもある

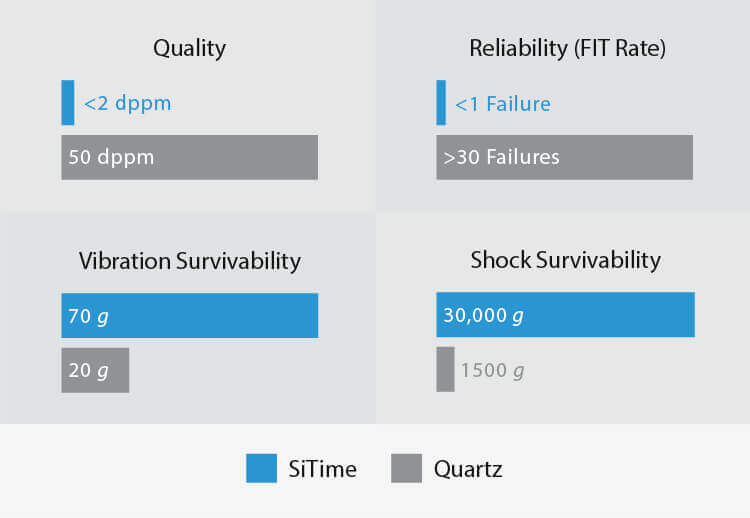

FPGA は、セットトップ ボックスや GPS 誘導兵器から海底や宇宙まで、さまざまなアプリケーションで使用されています。FPGA は、NRE コストの高さや市場投入までの時間の制約が厳しいためにカスタム ASIC の統合が現実的でない場合に、カスタマイズ可能なソリューションを提供します。安全で信頼性の高い動作を確保するために、FPGA 設計者は、安定したエンタープライズ環境から、幅広い温度変化、高振動、高圧力にさらされる環境まで、幅広い環境範囲をサポートする製品ラインを持つサプライヤに依存しています。