FPGAは、汎用I/Oを備えた当初のロジックとフリップフロップベースのファブリックをはるかに超えて進化しました。最新のFPGAは、組み込みメモリ、DSPブロック、 AIプロセッサ、そして高速相互接続を実現するネットワークオンチップを統合しています。また、多くのFPGAはマルチコアプロセッサを搭載しており、 AI/ MLワークロード向けに最適化されているものも少なくありません。

I/Oリングも進化し、ハードIPブロックと高速SerDesを統合することで、ギガビットイーサネット、PCIe、DDRメモリなどのインターフェースをサポートします。これらの追加機能により、現代のFPGAにおけるますます複雑化するクロック要件にも対応できます。

FPGAは複雑なクロック環境を表す

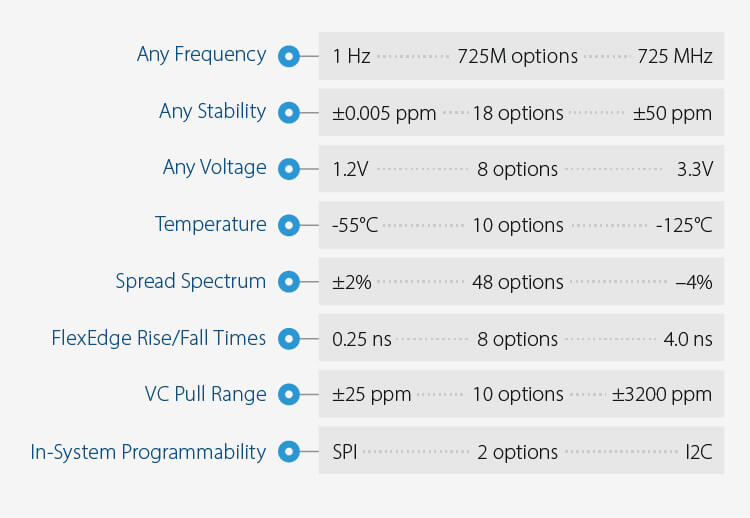

FPGAの機能拡張に伴い、クロック要件はより複雑化しています。こうした要求に応えるため、FPGAベンダーは複数のPLLとクロック管理機能を統合しており、多様なクロックソースへの需要が高まっています。

- 厳しい位相ノイズ要件を持つSerDesトランシーバー用のリファレンスクロック

- RTC、IEEE 1588、GNSSベースのアプリケーションのタイムキーピングとタイムスタンプ

- 組み込みPLL用の複数のリファレンスクロック

- I/Oバンクごとのリファレンスクロック

- ユーザーロジックのクロック

- 構成コントローラ、低速インターフェース、およびその他のシステム機能のクロックソースをサポート

SRAM ベースの FPGA では、通常、それぞれ独自のクロック ソースを持つ小さな CPU とフラッシュ メモリを使用して、構成に外部ロジックが必要になります。

FPGAとそのコンフィグレーションロジックは、高性能CPU、FPGAベースのアクセラレータ、トランシーバ、DRAM、その他のASSPと連携して動作します。これらのASSPはそれぞれ異なるクロック要件を備えています。これにより複雑なタイミング環境が生まれ、発振器から高度なクロック管理デバイスまで、包括的なクロックソリューションを提供するサプライヤーが求められます。

FPGAはどこにでもある

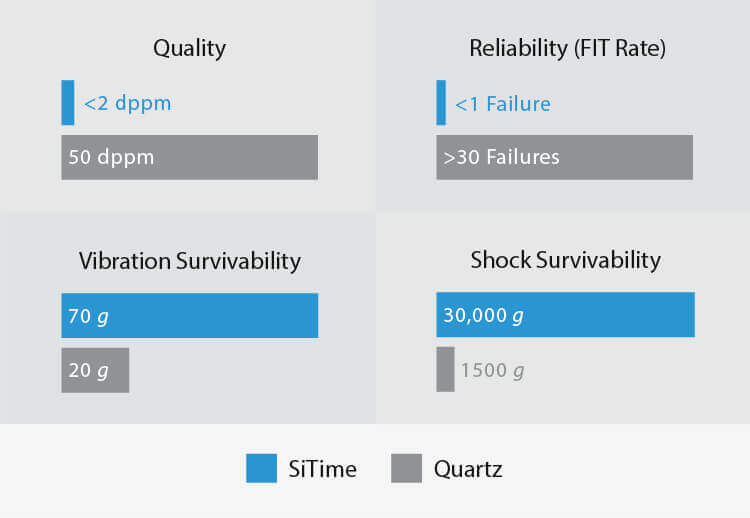

FPGAは、セットトップボックスやGPS誘導兵器から海底や宇宙まで、多様なアプリケーションで使用されています。NREコストの高さや市場投入までの期間の制約によりカスタムASICの統合が困難な場合に、FPGAはカスタマイズ可能なソリューションを提供します。安全で信頼性の高い動作を確保するために、FPGA設計者は、安定したエンタープライズ環境から、幅広い温度変化、高振動、高圧力にさらされる環境まで、幅広い環境に対応する製品ラインを持つサプライヤーに依存しています。