### **Precision Timing in Host Bus Adapter**

Host bus adapters (HBA) need an accurate and robust timing source to meet the desired high-bandwidth requirements. SiTime MEMS timing technology provides an extremely stable clock reference that has superior performance under harsh environmental conditions.

### **Key Considerations**

- Frequency stability

- Harsh environment

- Low jitter

- Multiple clocks

HBA platforms provide high-speed connections to memory and IO sub-systems for datacenter servers. Solid state disk-drives (SSD) are the most common form of high-speed, high-capacity memory devices used in datacenter applications. Host bus adapter platforms offer a scalable path to managing data storage capacity in server clusters deployed. HBA platforms decouple the compute servers from memory disk drive clusters and typically, a single HBA platform can service multiple compute servers.

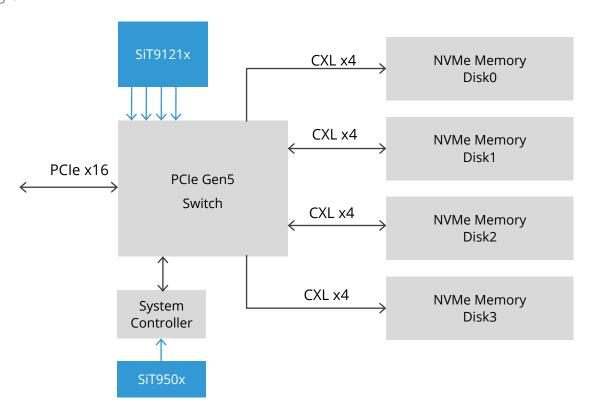

## Block Diagram

## **Precision Timing Solutions**

# Datacenter – Host Bus Adapter

The key technology trends driving HBA platform designs are distributed compute architectures, high density server clusters, high-capacity memory disk drivers and high-speed interfaces. All of these deliver high performance measured in memory and IO transfer rates.

High performance often translates to high power consumption and thermal management challenges. NVM Express (NVMe) technology based memory drives are also susceptible to failures under vibration. SiTime MEMS based oscillators and clock generators are ideally suited to deliver extremely stable, high frequency and low jitter clocks that are impervious to harsh environmental conditions.

Featured products – please refer to <u>SiTime.com</u> or <u>contact us</u> for more options.

| Туре                       | Product                      | Frequency                                       | Key Features                                                                                                                                                                                      | Key Values                                                                                                                                                                  |

|----------------------------|------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential<br>oscillator | <u>SiT9375</u>               | 25 to<br>644.5 MHz<br>(70 fs <sup>1</sup> IPJ)  | <ul> <li>±20 ppm to ±50 ppm frequency stability</li> <li>LVPECL, LVDS, HCSL</li> <li>1.8 V to 3.3 V</li> <li>-40°C to 105°C</li> <li>2.0 x 1.6 mm, 2.5 x 2.0 mm, 3.2 x 2.5 mm packages</li> </ul> | <ul> <li>Meets demanding jitter requirements</li> <li>Small PCB footprint, easier layout</li> <li>Easy design due to flexibility</li> <li>MEMS reliability</li> </ul>       |

|                            | <u>SiT9501</u>               | 25 to<br>644.5 MHz<br>(150 fs <sup>1</sup> IPJ) |                                                                                                                                                                                                   |                                                                                                                                                                             |

| Clock<br>Generator         | <u>SiT91211</u> <sup>2</sup> | 1 to 750 MHz<br>(200 fs <sup>1</sup> IPJ)       | <ul> <li>4 differential output clocks</li> <li>±20 ppm frequency stability</li> <li>LVDS, LVPECL, LPHCSL</li> <li>0.01 ps/mV PSRR</li> <li>-40°C to 105°C</li> <li>4 mm x 4 mm package</li> </ul> | <ul> <li>Simplifies Clock tree design with<br/>multiple low jitter clocks</li> <li>Programmable clocks add<br/>flexibility to complex clocking<br/>architectures</li> </ul> |

|                            | <u>SiT91213</u> ²            | 1 to 750 MHz<br>(90 fs <sup>1</sup> IPJ)        |                                                                                                                                                                                                   | <ul> <li>Better frequency stability and<br/>noise immunity in harsh<br/>environments</li> <li>Small PCB footprint, compact<br/>layout</li> </ul>                            |

<sup>&</sup>lt;sup>1</sup> 12 kHz to 20 MHz integration range <sup>2</sup> Please <u>contact SiTime</u> for availability