## Inphi PAM4 Performance when Driving Shared Reference Clocks

Test Case: Using one oscillator vs a multi-output clock generator to drive Inphi PAM4 DSPs

### Contents

| Introduction                                                | 1                                                                |

|-------------------------------------------------------------|------------------------------------------------------------------|

| Test Setup Overview                                         | 2                                                                |

|                                                             |                                                                  |

|                                                             |                                                                  |

|                                                             |                                                                  |

| Measurement Results                                         | 5                                                                |

| 4.1 Setup-1: Performance with SiT9365-156.25 MHz oscillator | 5                                                                |

| 4.2 Setup-2: Performance with quartz clock generator        | 7                                                                |

| Conclusion                                                  | 9                                                                |

| References:                                                 | 9                                                                |

|                                                             | Introduction<br>Test Setup Overview<br>Test Setup and Conditions |

## **1** Introduction

The Inphi Polaris and Vega 400G PAM4 DSP families [1] have dual die variants. In some cases, the reference clock (REFCLK) input for each die is brought out separately. In other cases, the reference clocks are connected together on the substrate (in the package) and only one reference clock input is brought out to the device pins.

For all these dual-die variants, it is preferable to use a single REFCLK source to minimize space, cost, and power in the end application.

The Inphi and SiTime applications teams have prepared and tested two reference clock configurations:

- 1. A SiTime Elite Platform<sup>™</sup> SiT9365 156.25 MHz oscillator [2] as a common reference clock for both dies this is the recommended configuration

- 2. A quartz clock generator on the Inphi Helios Evaluation Board (EVB) to drive the reference clock inputs of each die individually this is the default board configuration

The test for both configurations was conducted on the Inphi Helios Evaluation Platform at the Inphi lab. The purpose is to validate that the SiT9365 LVPECL differential clock can simultaneously drive two reference clock inputs of the Inphi PAM4 DSP while achieving optimum performance. All testing was done on the Inphi TX outputs at 28.125 Gbaud with PRBS7 pattern in Line PRBS Mode.

## 2 Test Setup Overview

The two reference clocks tested are described in Table 1. For comparison purposes, data was collected with a SiT9365-156.25 MHz oscillator as a shared reference clock and the quartz clock generator as the source for the two separate clock inputs of the Inphi PAM4 DSP on the Inphi Helios reference platform.

| Туре                        | Z      | Number of Clock<br>Outputs Used | Phase Jitter <sup>1</sup><br>(rms) fs |  |

|-----------------------------|--------|---------------------------------|---------------------------------------|--|

| SiTime SiT9365AI [2] 156.25 |        | 1                               | 225                                   |  |

| Quartz Clock Generator      | 156.25 | 2                               | 115                                   |  |

Note: 1 - Phase jitter integrated over 12 kHz to 20 MHz

The performance parameters measured during the tests are as shown in Table 2.

| Item | Parameters                                      | Test Setup and Conditions                                                                                                                                                                    |  |

|------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1a   | Eye diagram                                     | Setup-1: SiT9365 driving two reference clock inputs of PAM4                                                                                                                                  |  |

| 1b   | BER bath tub, eye width,<br>skew, random Jitter | DSP, TX lane differential outputs to Keysight Technologies DCA-<br>X 86100D WB scope (See Figure 2)                                                                                          |  |

| 2a   | Eye diagram                                     |                                                                                                                                                                                              |  |

| 2b   | BER bath tub, eye width,<br>skew, random jitter | Setup-2: Quartz clock generator two outputs driving reference<br>clock inputs of the PAM4 DSP; TX lane differential outputs to<br>Keysight Technologies DCA-X 86100D WB scope (See Figure 3) |  |

#### Table 2: Parameters tested and test conditions

The test setup details and conditions are covered in the following sections.

## 3 Test Setup and Conditions

All testing was done on the Inphi Helios evaluation platform. This platform uses two LVPECL clock outputs of the on-board quartz clock generator to drive the two reference clock inputs of the PAM4 DSP. This is the default board configuration.

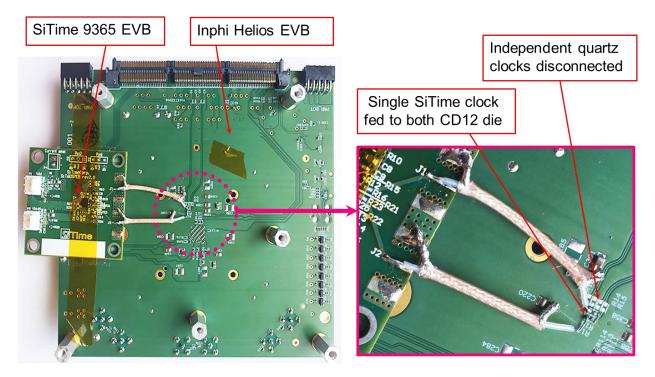

Test Setup-1: The Inphi Helios evaluation platform was modified such that the on-board quartz clock generator outputs were bypassed and a SiT9365-LVPECL oscillator output was wired-in to drive both reference clock inputs of the PAM4 DSP. This is shown in Figure 1.

## 💢 Inphi

Figure 1: A snippet of the test setup used to bypass the default configuration to drive both reference clock inputs of the Inphi PAM4 DSP with one SiT9365-LVPECL oscillator.

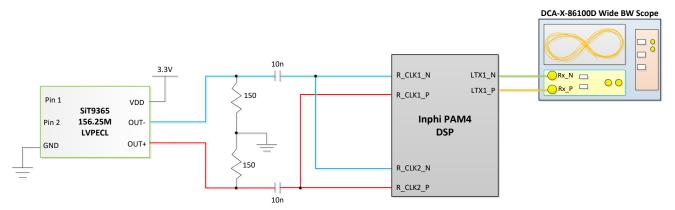

A block diagram of the complete Test Setup-1 is shown in Figure 2.

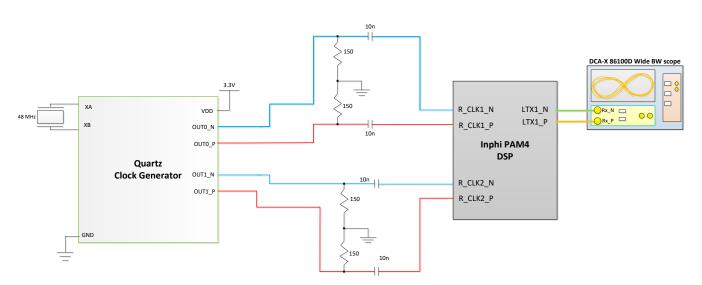

Test Setup-2: Two LVPECL outputs of the quartz clock generator each driving one of the two reference clock inputs of the PAM4 DSP is shown in the block diagram of Figure 3.

A Keysight Technologies DCA-X 86100D wide bandwidth scope was used to measure eye diagram and jitter related parameters on one of the 28.125 Gbaud PAM4 TX lanes of the Inphi PAM4 DSP.

### 3.1 Test Setup-1: SiT9365 driving two reference-clock inputs

# Figure 2: Test setup for measuring eye diagram and jitter on a 28.125 Gbaud TX lane of Inphi PAM4 DSP with both reference-clock inputs driven by a SiT9365-156.25 MHz oscillator.

After connecting one of the 28.125 Gbaud TX lanes to the DCA-X as illustrated in Figure 2, the PAM4 DSP was configured to send the PRBS7 pattern at 28.125 GBaud PAM4. The DCA-X was configured to display the eye diagram and measure the jitter/noise parameters on one of the TX lanes.

### 3.2 Test Setup-2: Quartz clock generator driving two reference clock inputs

# Figure 3: Test setup for measuring eye diagram and jitter on a 28.125 Gbaud TX lane of Inphi CD12 PAM4 PHY with each reference-clock input driven by the quartz clock generator.

After connecting one of the 28.125 Gbaud TX lanes to the DCA-X as illustrated in Figure 3, the PAM4 DSP was configured to send PRBS7 pattern at 28.125 Gbaud PAM4. The DCA-X was configured to display the eye diagram and measure the jitter/noise parameters on one of the data lanes.

## 4 Measurement Results

### 4.1 Setup-1: Performance with SiT9365-156.25 MHz oscillator

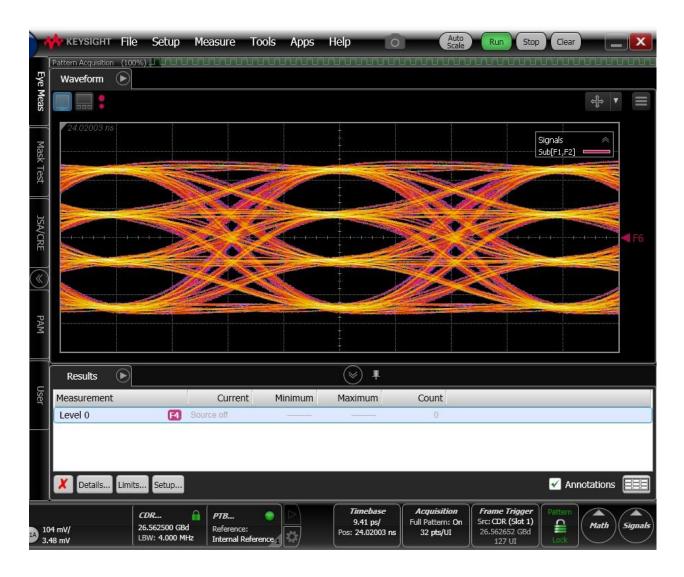

The eye diagram as measured on the DCA-86100D with the SiT9365 as a shared reference clock is shown in Figure 4.

|           | <b>KEYSIGHT</b> |                                               |                                     | ools Apps |                                                 | Auto<br>Scale                                  | Run Stop                                                      | Clear           |             |

|-----------|-----------------|-----------------------------------------------|-------------------------------------|-----------|-------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|-----------------|-------------|

| Eye Meas  | Waveform        | 9                                             |                                     |           |                                                 |                                                |                                                               |                 |             |

| Meas      |                 |                                               |                                     |           |                                                 |                                                |                                                               | ्म} <b>▼</b>    |             |

| Mask Test | 24.02396 ns     |                                               |                                     |           |                                                 |                                                |                                                               | Signals         |             |

| JSA/CRE   |                 |                                               |                                     |           |                                                 |                                                |                                                               |                 | <b>4</b> F6 |

| <u>()</u> |                 |                                               |                                     |           |                                                 |                                                |                                                               |                 |             |

| PAM       |                 |                                               |                                     |           |                                                 |                                                |                                                               |                 |             |

|           | Results 🧕       | $\mathbb{D}$                                  |                                     |           | - ⊗ ₽                                           |                                                |                                                               |                 |             |

| User      | Measurement     |                                               | Current                             | Minimum   | Maximum                                         | Count                                          |                                                               |                 |             |

|           | Level 0         | F4                                            | Source off                          |           |                                                 | D                                              |                                                               | ✓ Annotations   |             |

|           | 2 mV/<br>75 mV  | <i>CDR</i><br>26.562500 GBd<br>LBW: 4.000 MH: | PTB<br>Reference:<br>Internal Refer | ence      | <i>Timebase</i><br>9.41 ps/<br>Pos: 24.02396 ne | s Acquisition<br>Full Pattern: On<br>32 pts/UI | Frame Trigger<br>Src: CDR (Slot 1)<br>26.562678 GBd<br>127 UI | Pattern<br>Lock | Signals     |

Figure 4: PAM4 DSP TX lane eye diagram with a SiT9365-156.25 MHz clock as a shared reference clock.

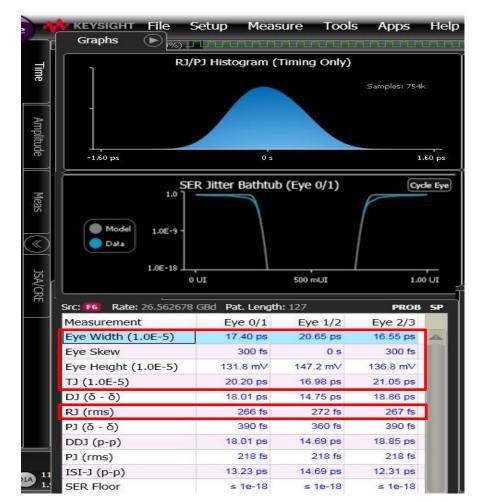

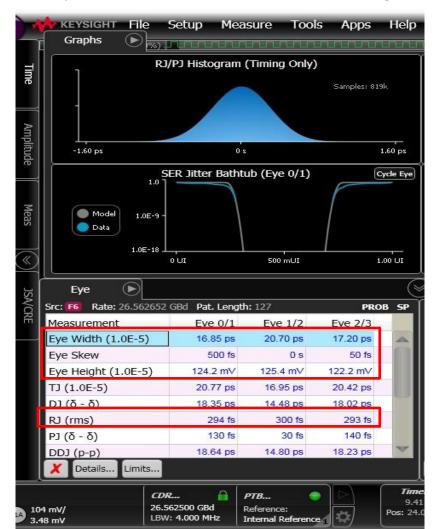

The jitter performance parameters for the PAM4 DSP TX lane are shown in Figure 5.

Figure 5: PAM4 DSP TX-1 data lane jitter performance parameters with a SiT9365-156.25 MHz clock as a shared reference clock.

Note that the reference clock contribution to the PHY TX lane eye is indicated by the following measured parameters:

- 1. Eye width

- 2. Eye skew

- 3. Eye height

- 4. SER jitter bathtub

- 5. Random jitter (RJ)

#### 4.2 Setup-2: Performance with quartz clock generator

The eye diagram as measured on the DCA-86100D with the quartz clock generator driving each of the two reference clock inputs independently (separate clock generator outputs) is shown in Figure 6.

Figure 6: PAM4 DSP TX lane eye with a quartz clock generator driving each of the two reference clock inputs independently.

The jitter performance parameters for the PAM4 DSP TX lane are shown in Figure 7.

# Figure 7: PAM4 DSP TX-1 data lane jitter performance parameters with a quartz clock generator driving each of the two reference-clock inputs.

Note that the reference clock contribution to the PHY TX lane eye is indicated by the following measured parameters:

- 1. Eye width

- 2. Eye skew

- 3. Eye height

- 4. SER jitter bathtub

- 5. RJ

### 5 Conclusion

The measurement data show that the SiTime SiT9365 MEMS LVPECL oscillator can drive two reference clock inputs of the Inphi 400G PAM4 DSP with no degradation in eye opening or jitter/noise performance.

| Performance Parameters                  | One MEMS SiT9365<br>Oscillator | Two Quartz<br>Clock Sources |

|-----------------------------------------|--------------------------------|-----------------------------|

|                                         | Eye 0/1                        | Eye 0/1                     |

| Eye width (ps)                          | 17.4                           | 16.85                       |

| Eye skew (fs)                           | 300                            | 500                         |

| Eye height (mV)                         | 131.8                          | 124.2                       |

| RJ, rms (fs)                            | 266                            | 294                         |

| Clock IDD (mA) without termination load | 85                             | 130*                        |

#### Table-3: Eye/Jitter performance of a CD12 TX lane

\*In a real application, if a clock generator or a single SiT9365 was not used, the alternative would have been two separate differential oscillators each consuming a minimum of 65 mA for a total of 130 mA.

The RJ (rms) component of the total jitter measurement is a key indicator of the reference clock contribution. In this test scenario, the MEMS SiT9365 oscillator outperforms the quartz clock generator used on the EVB as shown in Table 3.

In an SFP module, it is more common to use two oscillators instead of one clock generator for power, space and cost reasons. However, using one SiTime SiT9365-156.25 MHz oscillator, which can effectively drive two differential loads, versus two separate differential oscillators saves additional board space and BOM cost. In addition, the sub-system power dissipation and EMI/RFI is reduced because there is only one oscillator in the design and one differential pair of clock traces on the board.

## 6 References:

[1] Inphi PAM4 DSP datasheet: IN015050-CD02; <u>https://www.inphi.com/.</u>

[2] SiTime SiT9365 datasheet; <u>https://www.sitime.com/products/lvpecl-lvds-hcsl-oscillators/sit9365</u>.

#### Table 4: Revision History

| Version | Release Date | Change Summary |

|---------|--------------|----------------|

| 1.0     | 08/29/2018   | Original doc   |

#### SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation, Sept 2018. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

**Disclaimer:** SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

#### CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.