Systems are getting faster.

They have to.

The rapid escalation of broadband internet users and the growing use of bandwidth-hungry applications are placing more demands on data centers. The burgeoning self-driving car industry requires high-speed in-vehicle networking. These are just a few examples of increasing data throughput requirements.

Why Phase Noise & Jitter Specifications Matter

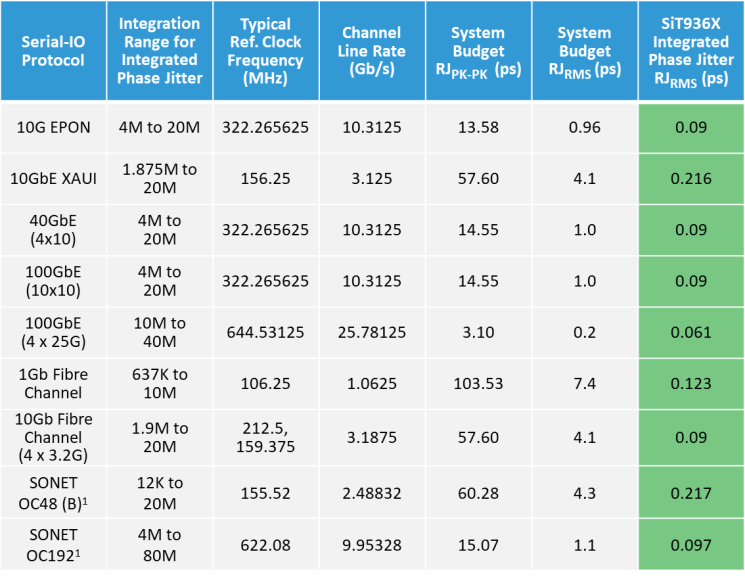

Timing plays a critical role in these high-speed systems, and phase noise and jitter (its time domain counterpart) are key oscillator specifications. Phase noise and jitter have a direct impact on system performance, affecting such parameters as bit error ratio (BER) in serial data systems. Wireless and GPS applications have stringent requirements for close-in phase noise (< 10 kHz offset), while serial communications applications such as those shown in the table below have specifications for RMS phase jitter.

Note 1: SONET does not separate DJ (deterministic jitter) and RJ (random jitter). Assumed all jitter is RJ.

This table shows several high-speed serial data communications protocols along with their line rates and typical reference clock frequencies. Also shown are the system jitter budgets and the integrated phase jitter for SiTime MEMS oscillators over the integration range for the standard. These system jitter budget numbers and integration ranges are based on governing standards such as IEEE 802.3 for Ethernet. The reference clock jitter specified in the governing standards is typically a guideline. A rule of thumb is that the clock is allocated 1/3 to 1/5 of the total system jitter budget. However, the switch/PHY chip vendors set the final parameter on clock jitter.

The jitter performance of SiTime’s MEMS oscillators has seen a dramatic improvement over the past 10 years, enabling robust timing solutions that provide plenty of headroom within the jitter budget. As an example, an implementation of 100GbE (shown in the table above) is 4 channels or lanes of 25.78125 Gb/sec of data transfer for an aggregate bandwidth of 103.125 Gb/sec. The system jitter budget is 0.2 ps RMS. The Elite Platform™ SiT936x oscillator supports this application with 0.061 ps jitter that is significantly lower than the system budget over the integration range of 10 MHz to 40 MHz.

SiTime's Elite Platform Oscillators

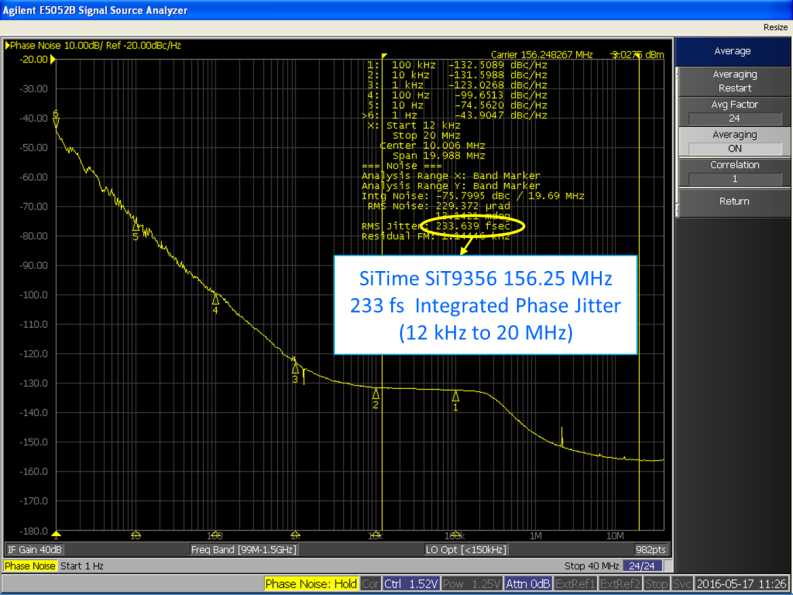

SiTime’s Elite Platform oscillators use a DualMEMS™ resonator combined with a highly optimized voltage controlled oscillator (VCO) and a low-noise, high-resolution TDC to achieve this phase noise performance. The plot below shows measured data of an Elite Platform SiT9356 oscillator with integrated phase jitter (IPJ) of only 233 femtoseconds (fs) RMS, integrated from 12 kHz to 20 MHz.

The integrated phase jitter (IPJ) of Elite Platform oscillators is significantly lower than the system budget of high-speed serial data communications applications. Moreover, the performance of Elite oscillators is maintained in wireless and serial data systems that are exposed to common environmental stressors such as shock, vibration, rapid temperature transients, and noisy power supplies. Immunity to these real-world conditions improves performance and eliminates loss of communications links.

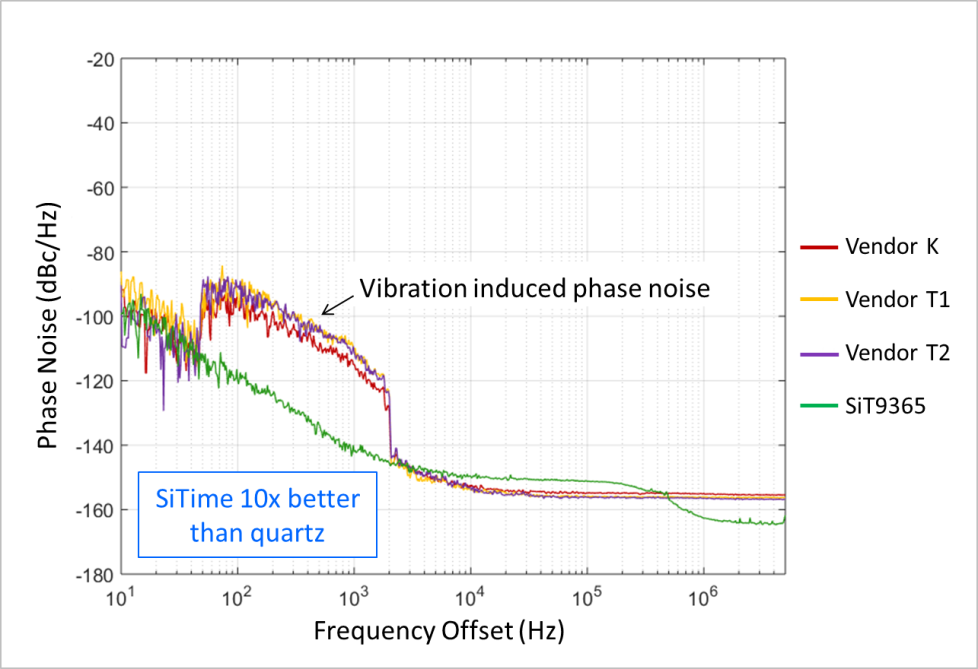

The plot below shows the phase noise of a MEMS SiT9365 oscillator compared to best-in-class quartz oscillators when subjected to vibration. The random vibration magnitude was 7.5g root mean square (RMS) over a frequency band of 15 Hz to 2 kHz.

The SiT9365 oscillator demonstrates about 10 times lower phase noise in this vibration frequency band. This is a significant benefit to communications systems deployed near train stations, subway stations, airports and many other locations that experience vibration.

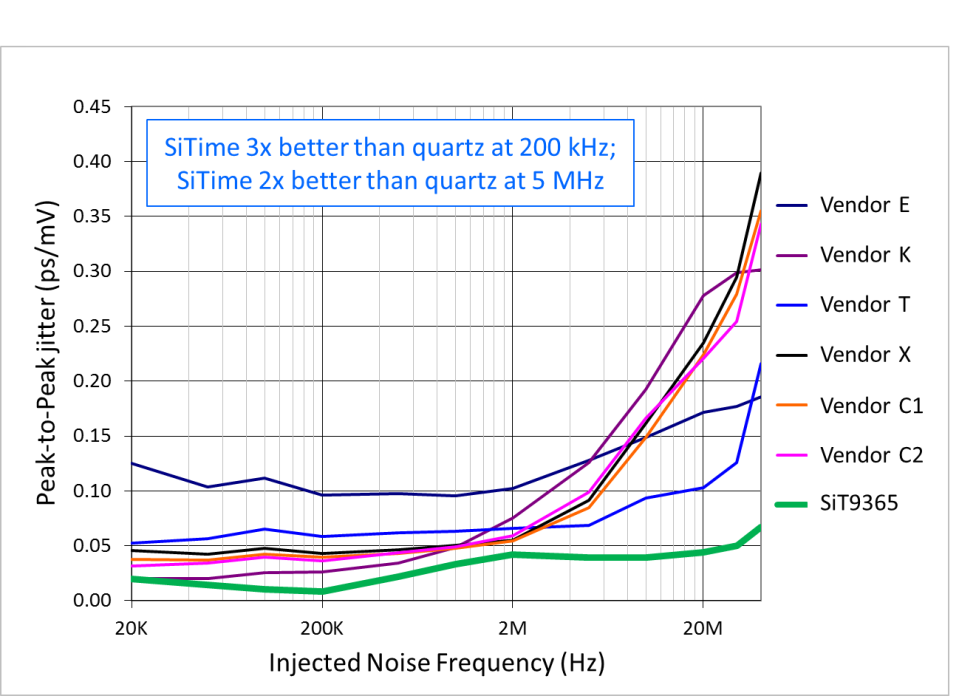

Noisy power supplies can be another source of jitter in high-speed systems. Noise on the power supply is often coupled to the output which can significantly degrade performance. The diagram below shows the power supply noise sensitivity of several differential oscillators measured in units of ps/mV. Lower numbers mean better performance. In this test, a 50-mV sine wave is AC-coupled onto the voltage supply pin, and the jitter resulting from this 50-mV sine wave is measured at the clock output.

The performance of the SiT9365 oscillator is two to three times better than the other quartz devices. To filter power supply noise, SiTime oscillators have integrated multiple power supply regulators on chip and have up to two stages of voltage regulation.

What more info?

Download our tech paper to learn about the Elite Platform architecture DualMEMS Temperature Sensing Technology. Or read our application note Clock Jitter Definitions and Measurement Methods for info on common types of jitter encountered in high-speed systems and guidelines on how best to measure jitter.